# Data Converters

## IC Handbook

#### DATASHEET ANNOTATION

GPS annotate datasheets in the top right hand corner of the first page, to indicate product status. These annotations are as follows:-

#### TARGET SPECIFICATION

This is the most tentative form of information and represents a very preliminary product specification. No actual design work on the product has started.

#### PRELIMINARY INFORMATION

The product is in design and development. The datasheet represents the product as it is understood but details may change.

#### ADVANCE INFORMATION

The product design is complete and final characterisation for volume production is well in hand.

#### No annotation

The product parameters are fixed and the product is available to datasheet specification in volume.

If you have any queries about the status of any GPS product, please contact your nearest GPS Customer Service Centre.

# DATA CONVERTERS

**IC Handbook**

## Foreword

GEC Plessey Semiconductors is recognised as a supplier of the very best in data conversion products meeting the requirements of a wide customer base. Access to a broad range of process technologies allows GPS to get the most out of its designs; so whether you need high speed, low cost, good linearity or whatever, there's a good chance that GPS can offer the right product to meet your needs. Recent developments have focused on video bandwidth ADCs and DACs and many of these devices are offered in support of our video processing ICs (as detailed in the Digital Video and DSP handbook).

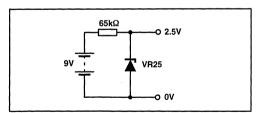

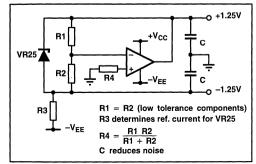

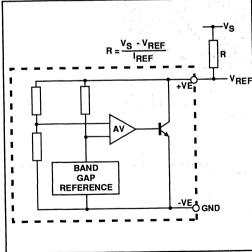

Increasingly the trend in many applications is for the data conversion function to become up-integrated into larger system chips. Indeed GPS offers a number of products with embedded data converters. But we also recognise that there is a need to maintain a range of standard ADCs and DACs and this handbook details those products which best serve the needs of our customers for general purpose and specialised higher performance data converter devices. GPS also maintains a comprehensive selection of voltage references - ranging from the latest ultra miniature 1% tolerance VR25 to the well established and extremely popular ZN458 and REFxx ranges.

And lastly, if you're not so familiar with data conversion techniques or want to know how to get the best out of your system designs then check out the Applications Notes section of this handbook. In there you will find a wealth of knowledge and advice based on the many years experience of our design and applications engineers.

# **Contents**

|               |                                       | PAGE |

|---------------|---------------------------------------|------|

|               |                                       |      |

| Product Ind   | ex                                    | 4    |

| Product List  | t - Alpha numeric                     | 7    |

| The Quality ( | Concept                               | 9    |

| Section 1:    | Video/Graphics DACs                   | 11   |

| Section 2:    | Advanced Function DACs                | 35   |

| Section 3:    | Advanced Function ADCs                | 61   |

| Section 4:    | Video and High Speed ADCs             | 95   |

| Section 5:    | Micropower Fixed Voltage References   | 145  |

| Section 6:    | Micropower Bandgap Voltage References | 165  |

| Section 7:    | Fixed Voltage References              | 179  |

| Section 8:    | Standard ECL                          | 193  |

| Section 9:    | Application Notes                     | 201  |

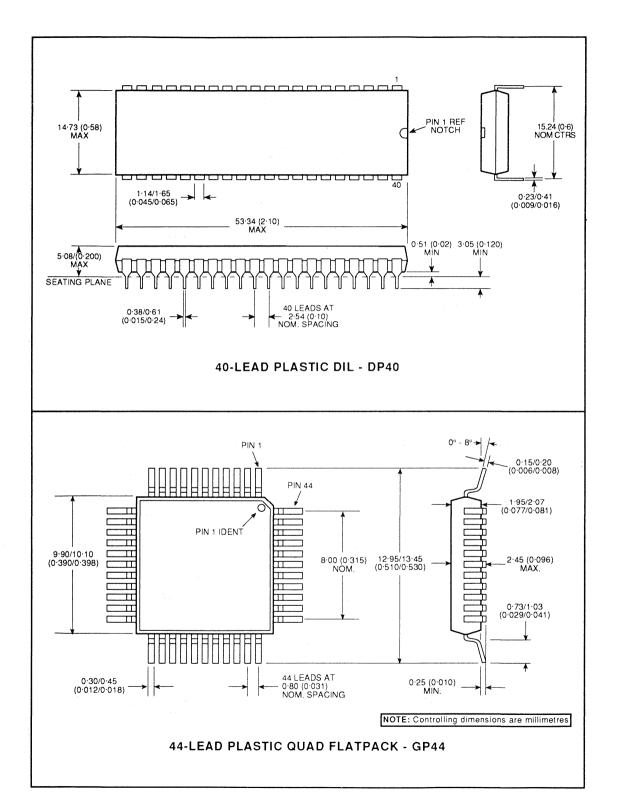

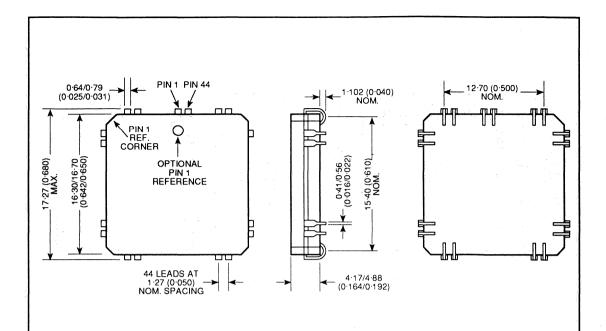

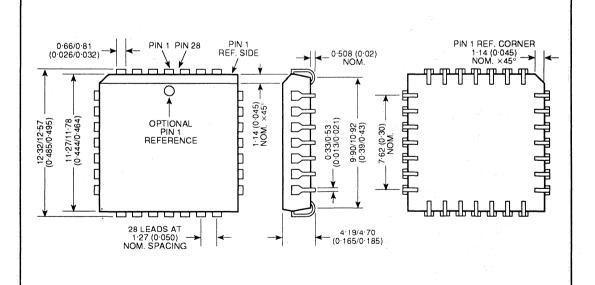

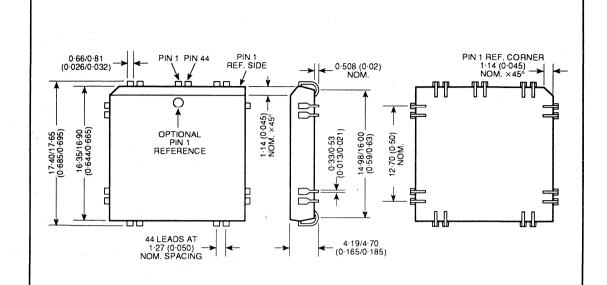

| Section 10:   | Package Outlines                      | 323  |

| Section 11:   | GPS Locations                         | 339  |

## Product index

## Video/Graphics DACs

| Type No. | Function                      | Minimum<br>clock rate<br>(MHz) | DAC mex.<br>rise time (ns)<br>(10% to 90%) | Process | Page |

|----------|-------------------------------|--------------------------------|--------------------------------------------|---------|------|

| MV95308  | 8-bit video DAC               | 30                             | 6.0                                        | CMOS    | 13   |

| MV95408  | 8-bit video DAC               | 50                             | 5.5                                        | CMOS    | 18   |

| SP98608  | 8-bit latched multiplying DAC | 450                            | 0.8                                        | Bipolar | 23   |

| VP101    | Triple 8-bit video DAC        | 30/50                          | 9.0                                        | CMOS    | 28   |

## Advanced Function DACs

| Type No. | Function                                | Linearity<br>error<br>(LSB) | Settling<br>time<br>(µs) | On-chip<br>reference | Special<br>features | Page |

|----------|-----------------------------------------|-----------------------------|--------------------------|----------------------|---------------------|------|

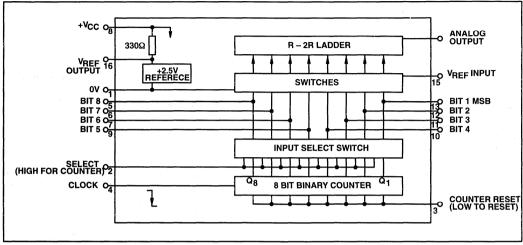

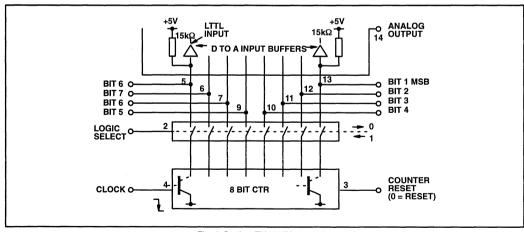

| ZN425    | 8-bit DAC/ADC                           | ±0.5                        | 1.0                      | Yes                  | 8-bit counter       | 37   |

| ZN426    | 8-bit DAC                               | ±0.5                        | 1.0                      | Yes                  | Low cost            | 43   |

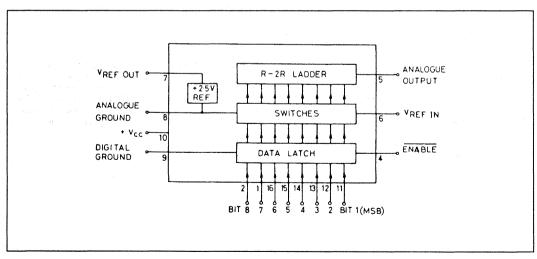

| ZN428    | 8-bit microprocessor-<br>compatible DAC | ±0.5                        | 0.8                      | Yes                  | Data latch          | 47   |

| ZN429    | 8-bit DAC                               | ±0.5                        | 1.0                      | No                   | Low cost            | 55   |

## Advanced Function ADCs

| Type Na. | Function                                | Linearity (<br>Options<br>(LSB) | Conversion<br>time<br>(µs) | On-chip<br>Clock | Special features                         | Page |

|----------|-----------------------------------------|---------------------------------|----------------------------|------------------|------------------------------------------|------|

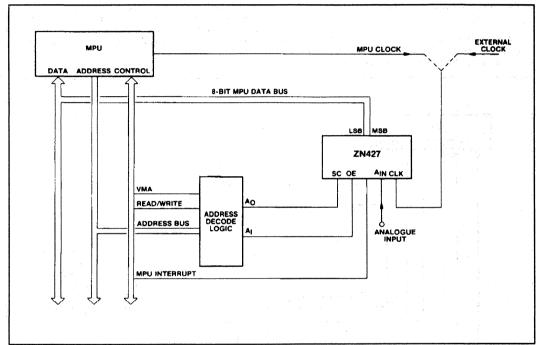

| ZN427    | 8-bit microprocessor-<br>compatible ADC | ±0.5                            | 10                         | No               | Three-state<br>data outputs              | 63   |

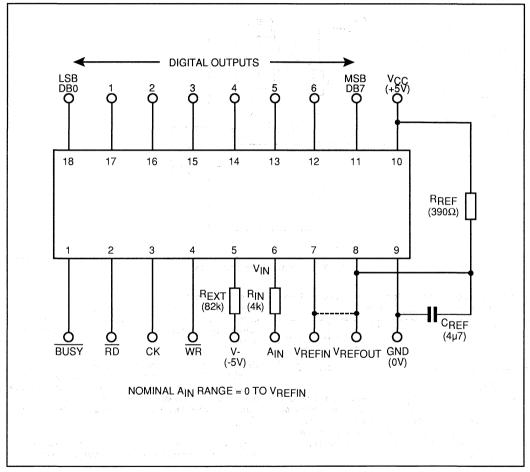

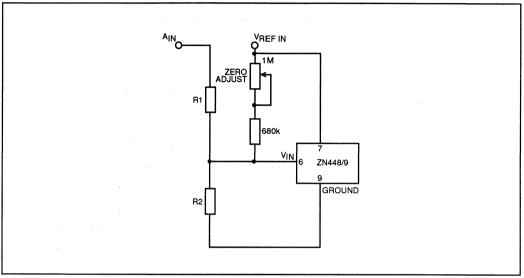

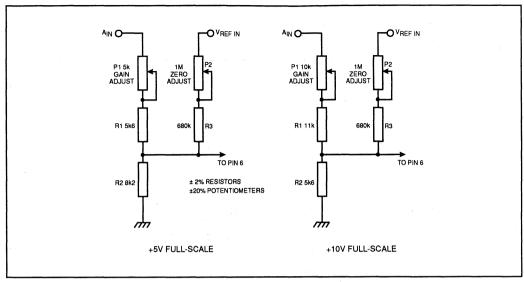

| ZN448    | 8-bit microprocessor-<br>compatible ADC | ±0.5                            | 9                          | Yes              | Three-state<br>data outputs              | 78   |

| ZN449    | 8-bit microprocessor-<br>compatible ADC | ±1.0                            | 9                          | Yes              | Three-state<br>data outputs,<br>low cost | 78   |

#### NOTE

All Advanced Function ADCs have on-chip reference

## Video and High Speed ADCs

| Type No. | Function                               | Minimum<br>clock rate<br>(MHz) | Process | Page |

|----------|----------------------------------------|--------------------------------|---------|------|

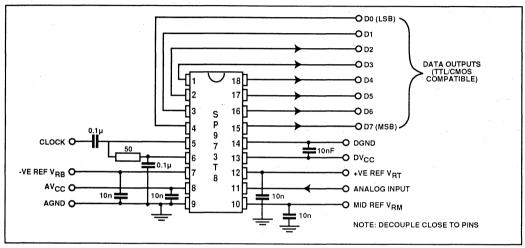

| SP973T8  | 8-bit flash ADC (TTL/CMOS outputs)     | 30                             | Bipolar | 97   |

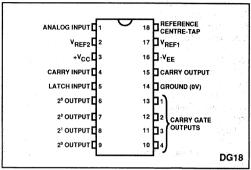

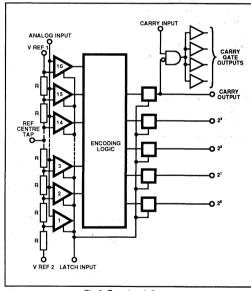

| SP97504  | 4-bit expandable ADC (replaces SP9754) | 110                            | Bipolar | 103  |

| SP97508  | 8-bit flash ADC                        | 110                            | Bipolar | 107  |

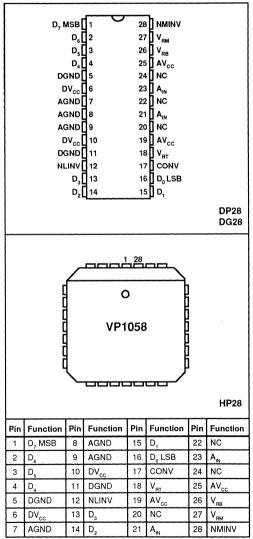

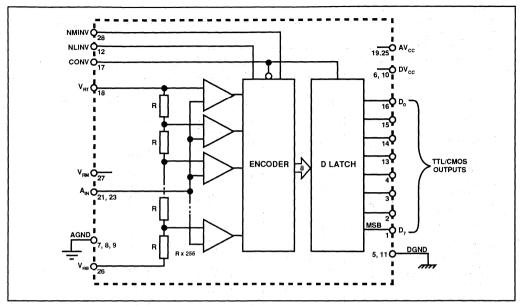

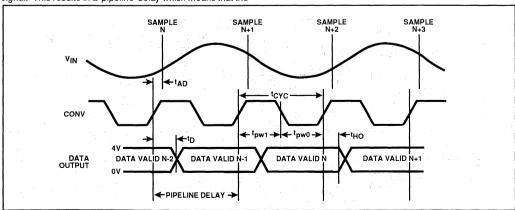

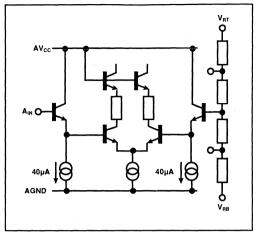

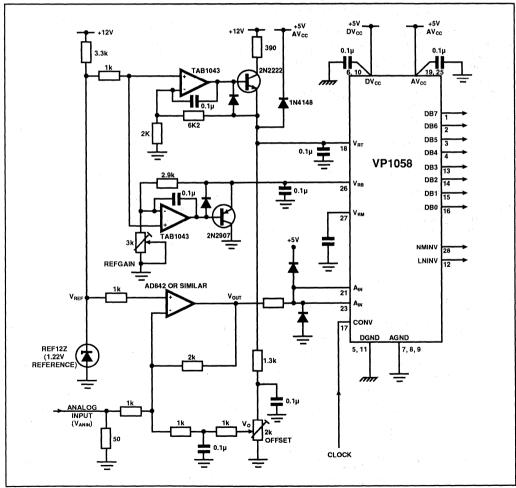

| VP1058   | 8-bit video ADC                        | 25                             | Bipolar | 114  |

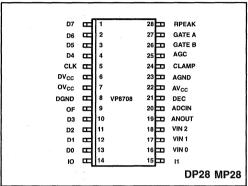

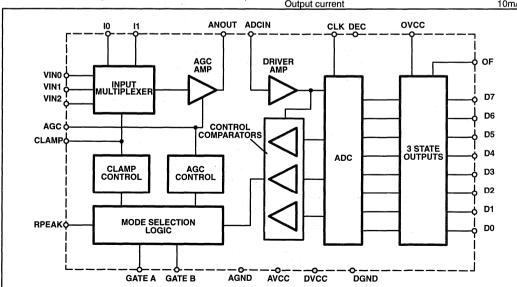

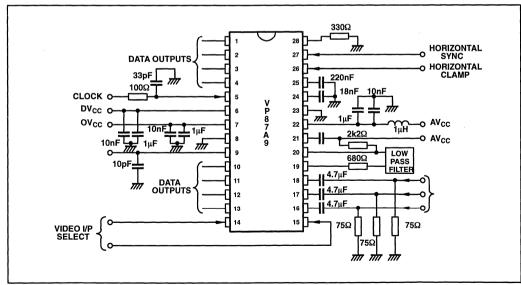

| VP8708   | 8-bit analog video input interface     | 30                             | Bipolar | 120  |

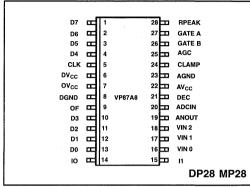

| VP87A8   | 8-bit analog video input interface     | 32                             | Bipolar | 128  |

| VP87A9   | 8-bit analog video input interface     | 30                             | Bipolar | 136  |

## Micropower Fixed Voltage References

| Type No. | Nominal<br>voltage<br>(V) | Guaranteed<br>Knee current<br>(μA) | Slope<br>resistance<br>(Ω) | Maximum<br>temperature<br>coefficient (ppm/°C) | Operating temperature range (°C) | Page |

|----------|---------------------------|------------------------------------|----------------------------|------------------------------------------------|----------------------------------|------|

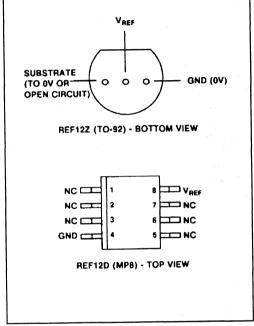

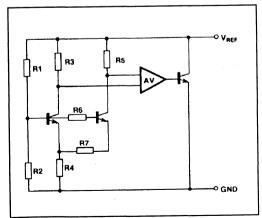

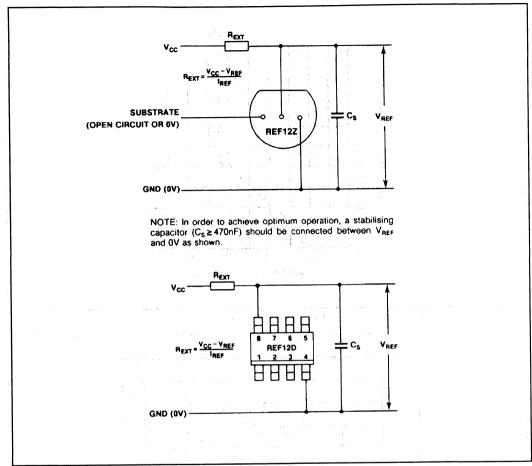

| REF12D   | 1.26                      | 90                                 | 4.0                        | 80                                             | -40 to +85                       | 147  |

| REF12Z   | 1.26                      | 90                                 | 4.0                        | 56                                             | -40 to +85                       | 147  |

| REF25D   | 2.50                      | 60                                 | 2.0                        | 80                                             | -40 to +85                       | 153  |

| REF25Z   | 2.50                      | 60                                 | 2.0                        | 110                                            | -40 to +85                       | 153  |

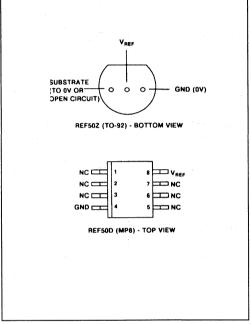

| REF50D   | 5.00                      | 60                                 | 3.5                        | 80                                             | -40 to +85                       | 159  |

| REF50Z   | 5.00                      | 60                                 | 3.5                        | 110                                            | -40 to +85                       | 159  |

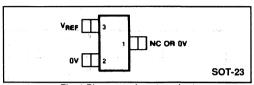

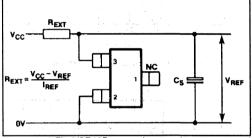

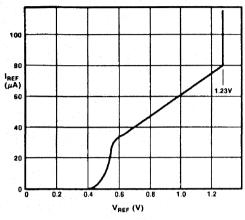

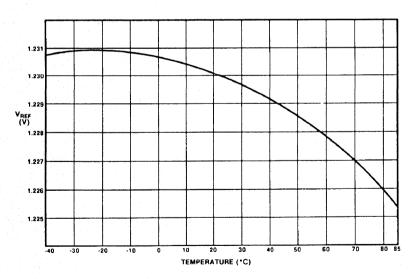

## SOT-23 Micropower Bandgap Voltage References

| Type No. | Nominal<br>voltage<br>(V) | Guaranteed<br>Knee current<br>(µA) | Slope<br>resistance<br>(12) | Maximum<br>temperature<br>coefficient (ppm/°C) | Operating temperature range (°C) | Page |

|----------|---------------------------|------------------------------------|-----------------------------|------------------------------------------------|----------------------------------|------|

| SR12D    | 1.23                      | 90                                 | 2.5                         | 125                                            | -40 to +85                       | 167  |

| SR25D    | 2.50                      | 80                                 | 2.0                         | 90                                             | 0 to +70                         | 170  |

| VR25     | 2.50                      | 80                                 | 0.2                         | 150                                            | -40 to +85                       | 173  |

## Fixed Voltage References

| Type No. | Nominal voltage (V) | Guara<br>currer<br>Min. | inteed<br>it (mA)<br>Mex. | Slope<br>resistance<br>((1)) | Maximum<br>temperature<br>coefficient (ppm/°C) | Operating temperature range (°C) | Page |

|----------|---------------------|-------------------------|---------------------------|------------------------------|------------------------------------------------|----------------------------------|------|

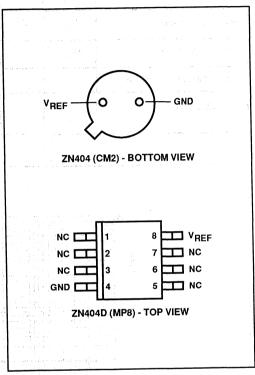

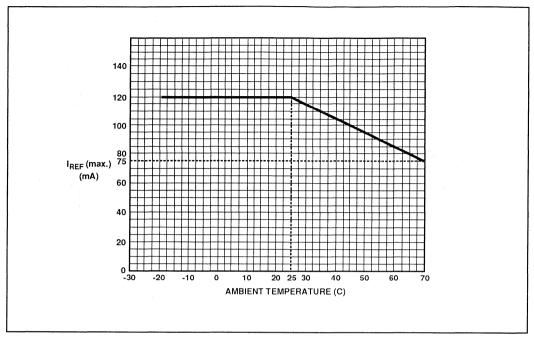

| ZN404    | 2.45                | 2                       | 120                       | 0.4                          | 145                                            | 0 to +70                         | 181  |

| ZN404D   | 2.45                | 2                       | 120                       | 0.4                          | 145                                            | -20 to +70                       | 181  |

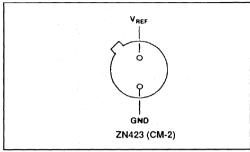

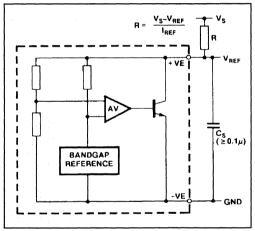

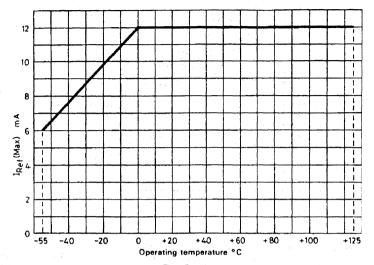

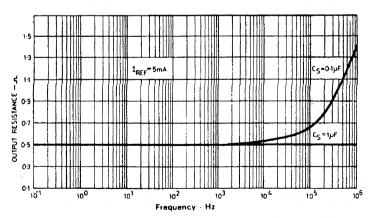

| ZN423    | 1.26                | 1.5                     | 12                        | 1.5                          | 101                                            | -55 to +125                      | 184  |

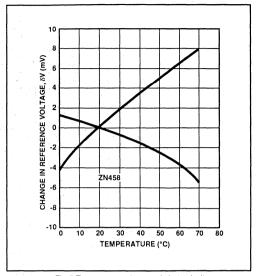

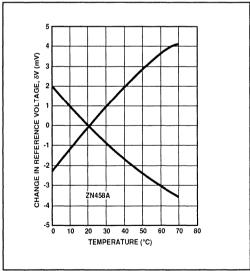

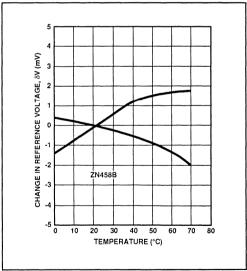

| ZN458    | 2.45                | 2                       | 120                       | 0.2                          | 99                                             | -20 to +70                       | 189  |

| ZN458A   | 2.45                | 2                       | 120                       | 0.2                          | 49                                             | -20 to +70                       | 189  |

| ZN458B   | 2.45                | 2                       | 120                       | 0.2                          | 29                                             | -20 to +70                       | 189  |

## Standard ECL

| Type No. | Function                      | Supply<br>voltage<br>(V) | Frequency<br>(MHz) | **** | Page |

|----------|-------------------------------|--------------------------|--------------------|------|------|

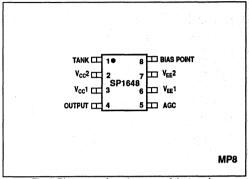

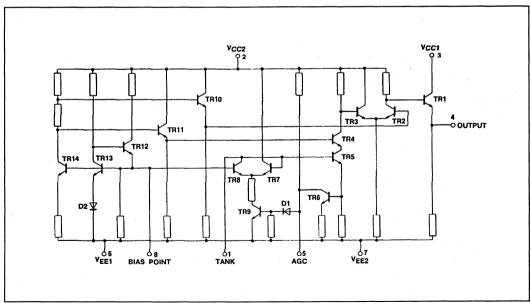

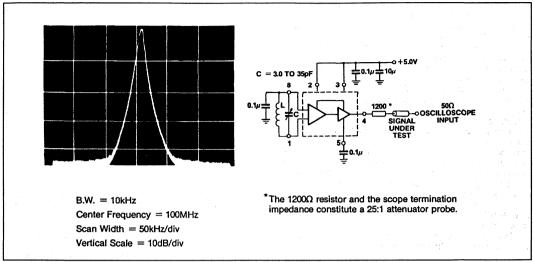

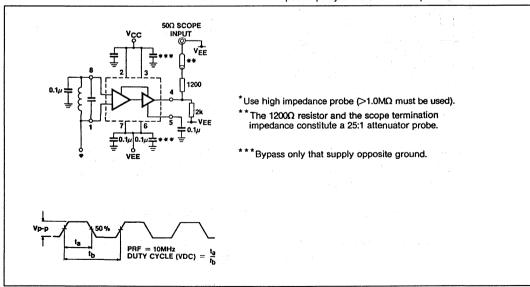

| SP1648   | Voltage controlled oscillator | +5 or -5.2               | 225                | 150  | 195  |

## Product List - Alpha numeric

| Type Number | Description                                            | Page |

|-------------|--------------------------------------------------------|------|

| MV95308     | 30MHz 8-bit video DAC                                  | 13   |

| MV95408     | 50MHz 8-bit video DAC                                  | 18   |

| REF12D/Z    | 1.26V low cost micropower precision voltage references | 147  |

| REF25D/Z    | 2.50V low cost micropower precision voltage references | 153  |

| REF50D/Z    | 5.00V low cost micropower precision voltage references | 159  |

| SP1648      | ECLIII voltage controlled oscillator                   | 195  |

| SP973T8     | 30MHz TTL/CMOS 8-bit flash ADG                         | 97   |

| SP97504     | 110MHz 4-bit expandable ADC                            | 103  |

| SP97508     | 110MHz 8-bit flash ADC                                 | 107  |

| SP98608     | 450MHz 8-bit latched multiplying DAC                   | 23   |

| SR12D       | 1.23V minieture micropower bandgap voltage reference   | 167  |

| SR25D       | 2.50V miniature micropower bandgap voltage reference   | 170  |

| VP101       | 30/50MHz triple 8-bit video DAC                        | 28   |

| VP1058      | 25MHz 8-bit video ADC                                  | 114  |

| VP8708      | 30MHz 8-bit analog video input interface               | 120  |

| VP87A8      | 32MHz 8-bit analog video input interface               | 128  |

| VP87A9      | 30MHz 8-bit analog video input interface               | 136  |

| VR25        | 2.50V precision micropower bandgap voltage reference   | 173  |

| ZN404/D     | 2.45V low noise voltage references                     | 181  |

| ZN423       | 1.26V low noise voltage reference                      | 184  |

| ZN425       | 8-bit DAC/ADC                                          | 37   |

| ZN426       | 8-bit DAC                                              | 43   |

| ZN427       | Microprocessor compatible 8-bit ADC                    | 63   |

| ZN428       | 8-bit latched input DAC                                | 47   |

| ZN429       | Low cost 8-bit DAC                                     | 55   |

| ZN448       | 8-bit microprocessor compatible ADC                    | 78   |

| ZN449       | 8-bit microprocessor compatible ADC                    | 78   |

| ZN458/A/B   | 2.45V low noise voltage references                     | 189  |

## The Quality Concept

Quality cannot be inspected into a product; it is only by careful design and evaluation of materials, parts and processes (followed by strict control and on-going assessment) that quality products will be produced.

All designs conform to standard layout rules, all processes are thoroughly evaluated and all new piece part designs and suppliers are investigated before authorisation for production use.

The same basic procedures are used on all products up to and including device packing. It is only then that extra operations are performed for certain customers in terms of lot qualification or release procedure.

By working to common procedures, all users benefit; the high reliability user gains the advantage of scale (hence improving the confidence factor in the quality achieved), while the volume user gains from the benefits of basic high reliability design concepts.

GEC Plessey Semiconductors (GPS) have the following factory approvals:

AQAP1

BS9450 (Capability Approval)

MIL-STD-883 Class B (In conformance with the requirements of MIL-STD-883, paragraph 1.2.1)

DESC (Department of Electronics Supply Center - Device approvals)

## Screening

Different screening procedures are carried out by GPS; a brief description of the differences involved are set out in Tables 1 and 2.

| Stage/<br>operation  | Standard product       | GPS<br>Hi-rel A                                                    | GPS<br>Hi-rel B | MIL-STD-883<br>Class B                                             | MIL-STD-883<br>Class S <sup>(1)</sup>                              |

|----------------------|------------------------|--------------------------------------------------------------------|-----------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| Wafer-fab            |                        |                                                                    |                 |                                                                    | Wafer-lot<br>accept<br>Method 5007                                 |

| Probe test           | 100%                   | 100%                                                               | 100%            | 100%                                                               | 100%                                                               |

| Visual inspect chips | Usually 2010<br>Cond.B | 2010<br>Cond.B                                                     | 2010<br>Cond.B  | 2010<br>Cond.B                                                     | 2010<br>Cond.A                                                     |

| Assemble             | V - 181                |                                                                    |                 |                                                                    | Includes 100%<br>bond pull                                         |

| Screen               | None                   | Method 5004<br>Class B                                             | As Table 2      | Method 5004<br>Class B                                             | Method 5004<br>Class S                                             |

| Test                 | 100%                   | 100%                                                               | 100%            | 100%                                                               | 100%                                                               |

| Conformance testing  | None                   | Method 5005<br>Class B<br>Group A<br>Group B<br>Group C<br>Group D | None            | Method 5005<br>Class B<br>Group A<br>Group B<br>Group C<br>Group D | Method 5005<br>Class S<br>Group A<br>Group B<br>Group C<br>Group D |

Table 1

MIL-STD-883 Class S/ESA SCC9000: GPS has supplied numerous devices to customer specifications for Space and Satellite applications. Please contact your local GPS sales office for information.

| Stage/<br>operation                    | GPS Hi-rel B<br>(References are to MIL-STD-863)     | MIL-STD-883 Class B<br>Method 5004 <sup>th</sup>    |

|----------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| Internal Visual                        | Method 2010 Test Condition B 100%                   | Method 2010 Test Condition B 100%                   |

| Stabilisation Bake                     | Method 1008<br>24Hrs at Condition C 100%            | Method 1008<br>24Hrs at Condition C 100%            |

| Temperature Cycling                    | Method 1010 Test Condition C 100%                   | Method 1010 Test Condition C 100%                   |

| Constant Acceleration                  | Method 2010<br>Condition E Y1 only 100%             | Method 2010<br>Condition E Y1 only 100%             |

| Visual Inspection                      |                                                     | 100%                                                |

| Initial Electrical                     | Those parameters requiring Delta calculations. 100% | Those parameters requiring Delta calculations. 100% |

| Burn-In                                | Method 1015<br>160Hrs at 125°C min. 100%            | Method 1015<br>160Hrs at 125°C min. 100%            |

| Post Burn-In Electrical Test           | Full Electrical Test to Guarantee datasheet, 100%   | Those parameters requiring Delta calculations. 100% |

| PDA Calculation                        | 5% max. All lots                                    | 5% max. All lots                                    |

| Final Electrical Test                  | Done as Post Burn-In Test. 100%                     | Full Group A tests as Method 5005. 100%             |

| Seal (a) Fine<br>Seal (b) Gross        | Method 1014 100%                                    | Method 1014 100%                                    |

| Qualification/Quality Conformance Test |                                                     | Method 5005 Class B<br>Samples as necessary         |

| External Visual                        | GPS Spec. sample                                    | Method 2009 100%                                    |

#### 2. See Section 5 for further information.

# Section 1 Video/Graphics DACs

## MV95308 30MHz 8-BIT CMOS VIDEO DAC

The MV95308 is a CMOS 8-bit, 30MHz Digital to Analog converter, designed for use in both video graphics and general digital television applications.

A very low external component count has been achieved by including the loop amplifier and reference voltage source on chip.

The device contains a data input register and registered video controls (BLANK, REFWHITE, OVERBRT and SYNC). These control inputs and associated internal circuitry allows the MV95308 to be used in video graphics systems by providing the necessary video pedestal levels. The STRDAC input allows the video pedestals to be disabled in conventional DAC applications.

This device is capable of directly driving 75 $\Omega$  lines with standard RS-343A or RS-170 video levels, using the appropriate  $R_{SET}$  external resistor.

Pull up resistors have been added to tie all unused control inputs into their inactive (High) states.

#### **FEATURES**

- Low Power Consumption (180mW Typ)

- 30MHz Pipeline Operation

- ±1 LSB Differential Linearity Error

- ±1 LSB Integral Linearity Error

- RS-343A/RS-170 Compatible Levels

- On Chip Reference Voltage Source

- Guaranteed Monotonic

- Drives 75Ω Loads Directly

- Single 5V Power Supply

#### ORDERING INFORMATION

MV95308 ADG (Military - Ceramic DIL Package)

MV95308 CDP (Commercial - Plastic DIL Package)

MV95308 CMP (Commercial - Miniature Plastic DIL

Package)

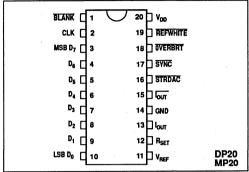

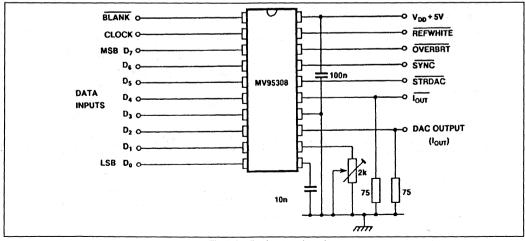

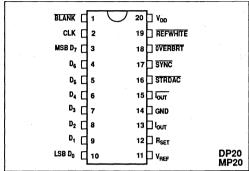

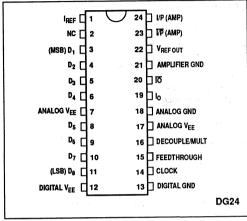

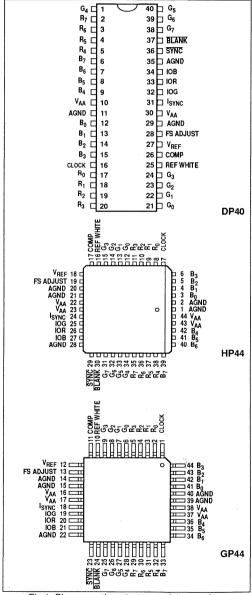

Fig.1 Pin connections - top view

#### **APPLICATIONS**

- Data Conversion (general)

- Computer Graphics

- Waveform Synthesis

- Consumer TV

- Instrumentation

ABSOLUTE MAXIMUM RATINGS (Reference to GND)

DC Supply Voltage, V<sub>DD</sub> -0.3 to +7V

Digital Input Voltage -0.3 to V<sub>DD</sub> +0.3V

Analog Output Short Circuit Duration

Ambient Operating Temperature A grade C grade

Storage Temperature Range -55°C to +125°C

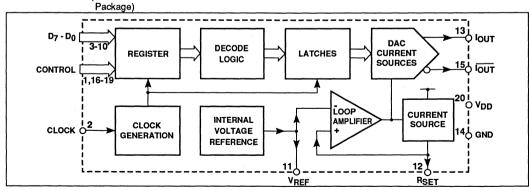

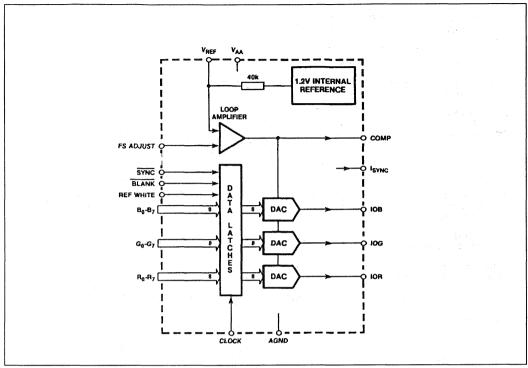

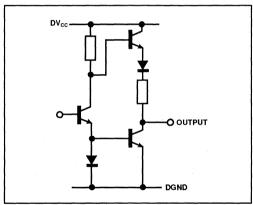

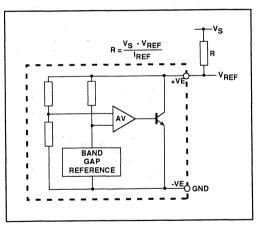

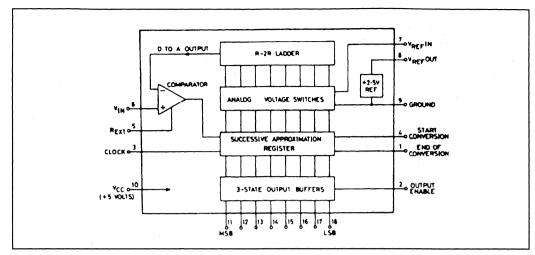

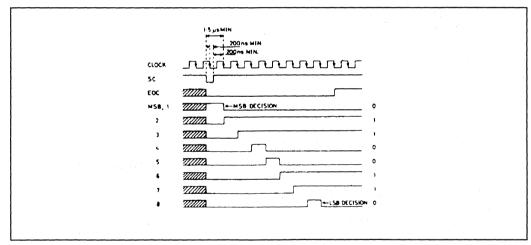

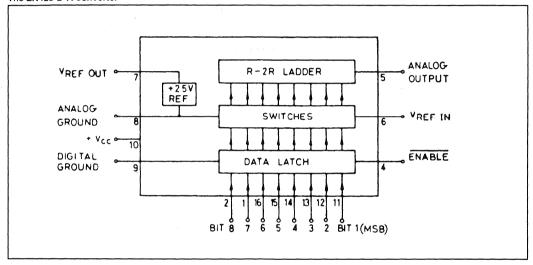

Fig.2 Block diagram of MV95308

#### MV95308

ELECTRICAL CHARACTERISTICS

These characteristics are guaranteed over the following conditions (unless otherwise stated):

As specified in recommended operating conditions. Full temperature range: A grade = -55°C to +125°C, C grade = 0 to 70°C DC CHARACTERISTICS

| DO OTIATAO TENIO TICO                          |                  |              | ,            |               |                      | ·          | ·                                      |

|------------------------------------------------|------------------|--------------|--------------|---------------|----------------------|------------|----------------------------------------|

| Parameter                                      | Symbol           | Temp<br>(°C) | Min.         | Value<br>Typ. | Max.                 | Units      | Conditions                             |

| Resolution                                     |                  | Full         | 8            |               |                      | Bits       |                                        |

| Integral linearity error                       | . INL            | 25<br>Full   |              | ±0.5          | ±1                   | LSB<br>LSB |                                        |

| Differential linearity error                   | DNL              | 25<br>Full   |              | ±0.5          | ±1                   | LSB<br>LSB |                                        |

| Gain error                                     |                  | 25           |              | ±1%           | ±5%                  | %          | Of full scale                          |

| Analog output                                  |                  |              |              |               |                      |            |                                        |

| Grey scale current range                       |                  | 25           |              | 8.8<br>255    |                      | mA<br>LSB  |                                        |

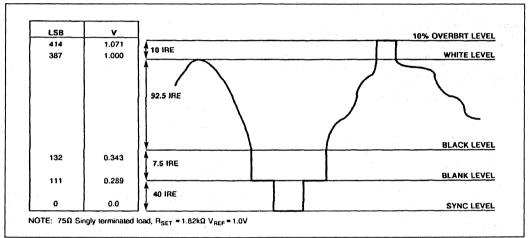

| 10% Over Bright level relative to White level  |                  | 25           | 26           | 27<br>10      | 28                   | LSB        |                                        |

| White level relative to Blank level            |                  | 25           | 275          | 276<br>100    | 277                  | LSB<br>IRE | 75Ω singly                             |

| Black level relative to Blank level            |                  | 25           | 20           | 21<br>7.5     | 22                   | LSB        | terminated load                        |

| White level relative to Black level            |                  | 25           |              | 255<br>92.5   |                      | LSB        | $R_{SET} = 1.8k\Omega$ (graphics mode) |

| Blank level                                    |                  | 25           | 107          | 111<br>40     | 115                  | LSB        |                                        |

| Sync level                                     |                  | 25           |              | 0             |                      | LSB        |                                        |

| LSB size                                       | LSB              | 25           |              | 2.58          |                      | mV         |                                        |

| Output compliance                              | V <sub>oc</sub>  | 25           | -0.3         |               | +1.5                 | V .        |                                        |

| Digital inputs                                 |                  |              |              |               |                      |            |                                        |

| High level I/P voltage                         | V <sub>IH</sub>  | 25           | 3            |               | V <sub>DD</sub> +0.3 | V          |                                        |

| Low level I/P voltage                          | V <sub>IL</sub>  | 25           | GND-0.3      |               | 12                   | · V        |                                        |

| High level I/P current                         | I <sub>IH</sub>  | 25           |              |               | +1                   | μΑ         |                                        |

| Low level I/P current                          | ا ال             | 25           |              |               | -1                   | μA         |                                        |

| Internal voltage reference (V <sub>REF</sub> ) | V <sub>REF</sub> | 25<br>Full   | 0.95<br>0.90 | 1.0           | 1.05<br>1.10         | V          | 4.                                     |

| V <sub>REF</sub> temperature coefficient       |                  |              |              | 40            |                      | ppm/°C     |                                        |

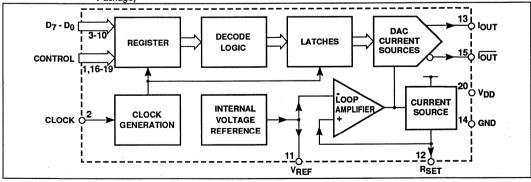

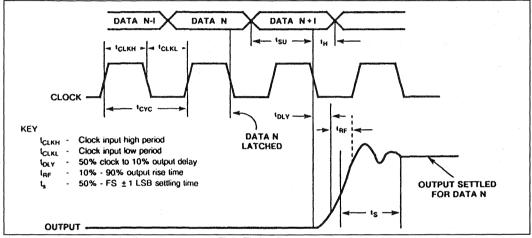

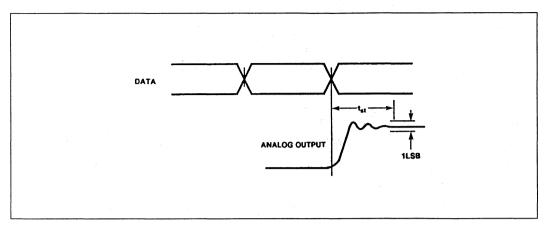

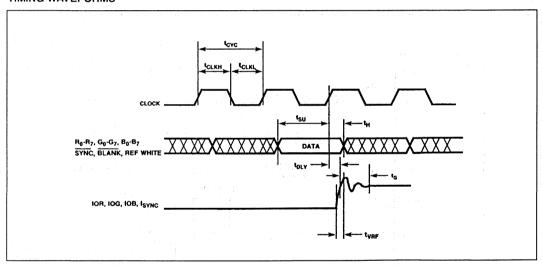

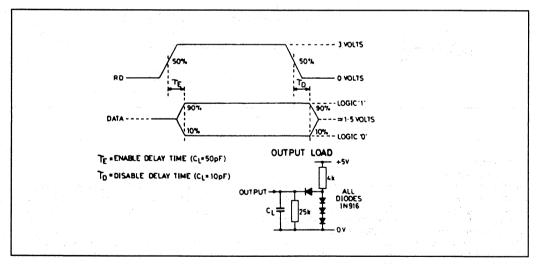

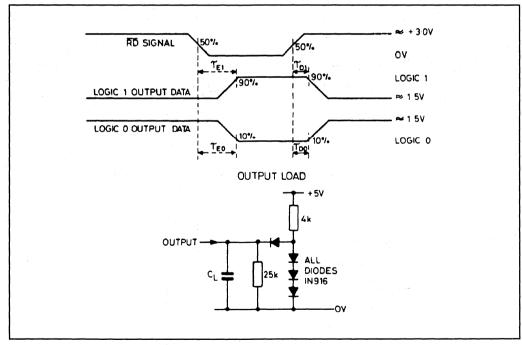

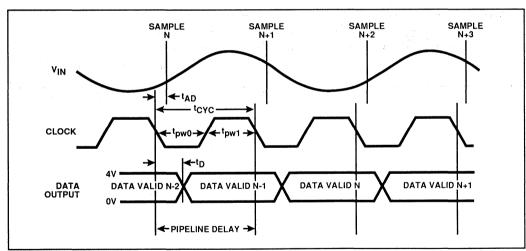

#### AC CHARACTERISTICS (Refer to Fig. 3)

| Parameter                      | Symbol            | Temp<br>(°C) | Min. | Value<br>Typ. | Max. | Units    | Conditions                  |

|--------------------------------|-------------------|--------------|------|---------------|------|----------|-----------------------------|

| Max clock rate                 | f <sub>MAX</sub>  | Full         | 30   |               |      | MHz      | maximum<br>guaranteed freq. |

| Clock high time                | t <sub>CLKH</sub> | 25           | 10   |               |      | ns       |                             |

| Clock low time                 | t <sub>CLKL</sub> | 25           | 10   |               |      | ns       |                             |

| Data and control setup time    | t <sub>SU</sub>   | 25           | 8    |               |      | ns       | 1000                        |

| Data and control hold time     | t <sub>H</sub>    | 25           | 2    |               |      | ns       |                             |

| Analog output delay            | t <sub>DLY</sub>  | 25           | ~ -  | 10            | 1    | ns       |                             |

| Analog output rise/fall time   | t <sub>RF</sub>   | 25           |      | 3             | 6    | ns       |                             |

| Analog output settling time    | ts                | 25           |      | 15            |      | ns       |                             |

| Glitch energy                  |                   | 25           |      | 100           |      | pV-sec   |                             |

| V <sub>DD</sub> supply current | IDD               | 25           |      | 30<br>36      |      | mA<br>mA | fc = 15MHz<br>fc = 30MHz    |

| THERMAL |  |  |

|---------|--|--|

|         |  |  |

|         |  |  |

| Thermal Resistance              | DP | MP |      |

|---------------------------------|----|----|------|

| Chip to case θ <sub>iC</sub>    | 20 | 30 | °C/W |

| Chip to ambient θ <sub>jA</sub> | 75 | 93 | °C/W |

#### RECOMMENDED OPERATING CONDITIONS

| LOOMINENDED OF EFFATING CON                                | 21110113        |

|------------------------------------------------------------|-----------------|

| R <sub>LOAD</sub> (I <sub>OUT</sub> and I <sub>OUT</sub> ) | 75Ω             |

| $V_{DD}$                                                   | $5.0V \pm 0.5V$ |

| R <sub>SET</sub> (graphics applications)                   | 1.8kΩ           |

| Rect (straight DAC applications)                           | 1.2k0           |

#### CIRCUIT DESCRIPTION

As illustrated in the function block diagram, Fig. 2, the MV95308 contains an 8-bit D-to-A converter, input registers, a loop amplifier and a voltage reference.

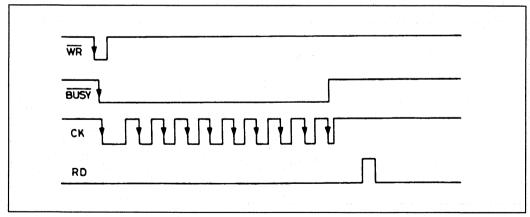

On the falling edge of each clock cycle, as shown in Fig. 3, eight data bits are latched into the device and passed to the 8-bit D-to-A converter. Also latched on the falling edge of the clock signal, the SYNC and BLANK inputs add the necessary weighted currents to the analog outputs to produce the required output levels for use in video applications. Table 1 details how the SYNC, BLANK, REFWHITE and OVERBRT inputs modify the DAC output levels.

To obtain a high data throughput rate, the decoding logic of the MV95308 is fully pipelined. This introduces a one clock cycle delay between the latching of the input data and the resultant DAC output. It also ensures synchronisation of the internal data and a minimal output glitch energy.

The DAC employed by the MV95308 eliminates the need for precision component ratios by using segmented architecture in which equal weight bit currents are either routed to lout or lout. The use of identical current sources and current steering their outputs means that monotonicity is guaranteed.

The MV95308 eliminates the need for an external voltage reference by providing a nominally 1.0V reference on chip. An on-chip loop amplifier also provides stability of the full scale output current against power supply and temperature variations. The full scale output current is set by an external resistor R<sub>SET</sub>. By adjustment of this value it is possible to implement RS-343A or RS-170 video levels as explained in the application notes.

Fig.3 Timing diagram

| Description    | STRDAC | SYNC | BLANK        | REFWHITE | OVERBRT | OUTPUT<br>DATA | I <sub>OUT</sub><br>(LSB) |

|----------------|--------|------|--------------|----------|---------|----------------|---------------------------|

| REFWHITE + 10% | . 1    | 1    | 1            | 0        | 0       | Х              | 414                       |

| REFWHITE       | 1      | 1    | 1            | 0        | 1       | Х              | 387                       |

| FULL WHITE     | 1      | 1    | 1            | 1        | 1       | \$FF           | 387                       |

| OVERBRIGHT     | 1      | 1    | 1            | 1        | 0       | DATA           | DATA +<br>132 + 27        |

| FULL BLACK     | 1      | 1    | 1            | 1        | 1       | \$00           | 132                       |

| BLANK          | 1      | 1    | 0            | Х        | Х       | Х              | 111                       |

| DATA-SYNC      | 1      | 0    | • . <b>1</b> | 1        | : 1     | DATA           | DATA + 21                 |

| SYNC           | 1      | 0    | 0            | х        | х       | х              | : 0                       |

| STRDAC MODE    | 0      | Х    | 1            | 1        | Х       | DATA           | DATA                      |

Table 1: Video output truth table

#### MV95308

| Pin   | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2     | CLK                                 | The clock input. The falling edge of the clock latches the DATA, BLANK, SYNC, OVERBRT and REFWHITE inputs into the logic pipeline. The decoded data will be latched into the DAC output 1 clock cycle later. The clock frequency determines the update rate of the DAC output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3-10  | D <sub>7</sub> -D <sub>0</sub>      | The data inputs. D <sub>0</sub> is the least significant bit (LSB). The coding is in straight binary only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13,15 | l <sub>out</sub> , l <sub>out</sub> | The current output and its complement. These are the high impedance current source outputs of the DAC capable of driving a $75\Omega$ load up to a voltage of 1.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14    | GND                                 | Analog ground for the DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 20    | $V_{DD}$                            | Analog power for the DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11    | V <sub>REF</sub>                    | The output of the internal voltage reference generator. This output is nominally 1V, and should be decoupled with a 10nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12    | R <sub>SET</sub>                    | The full scale adjust control. The R <sub>SET</sub> resistor is connected from this pin to ground. An internal loop amplifier adjusts a reference current flowing through the R <sub>SET</sub> resistor so that the voltage across the resistor is equal to the V <sub>REF</sub> voltage. This reference current has a weighting equal to 16 LSB's.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1     | BLANK                               | The composite blank control input. A logical zero on this input removes the Black pedestal from the I <sub>OUT</sub> output, whilst forcing the internal data to the DAC to \$00. This input is latched on the clock falling edge and will override the REFWHITE and OVERBRT inputs. The Black pedestal is 7.5 IRE units (actually 21 LSB's). If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17    | SYNC                                | The composite sync control input. A logical zero on this input removes the Blank pedestal from the I <sub>OUT</sub> output. The Blank pedestal is nominally 40 IRE units (actually 111 LSB's). The SYNC input does not override any other control lines. This input is latched on the clock falling edge. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19    | REFWHITE                            | The reference white level control input. A logical zero on this input overrides the input data, forcing the data to \$FF. The BLANK input will override this input. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18    | OVERBRT                             | The 10% overbright control input. A logical zero on this input switches the Overbright pedestal into the I <sub>OUT</sub> output. The Overbright pedestal is 10 IRE units (actually 27 LSB's). This input does not override any other input. The BLANK input overrides this input. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16    | STRDAC                              | The straight DAC control input. A logical zero on this input causes the Black, Blank and Overbright pedestals to be disabled, removing them from both $I_{OUT}$ and $I_{OUT}$ . This allows the DAC contribution to the output to be extended to a full 1 Volt. To obtain this extra DAC range, it is necessary to reduce the $R_{\rm SET}$ resistor value, see application notes. The BLANK the REFWHITE inputs may still be used to force the input data to \$00 or \$FF respectively. With the \$TRDAC\$ pin held low the output current can be calculated from:  Output current = Data x 1 LSB  Where 1 LSB= $\frac{V_{\rm REF}}{16~\rm x~R_{\rm SET}}$ Full scale = 255 LSB $V_{\rm REF}$ = 1.0V typ.  The exact value of 1 LSB must be calculated from the full scale output. If left open circuit this input is internally tied high and the device will be configured for video graphics. In this mode the output current can be calculated from: |

|       |                                     | Output current = (DATA + 21 + 111) x 1 LSB<br>V <sub>REF</sub> = 1.0V typ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### APPLICATIONS INFORMATION

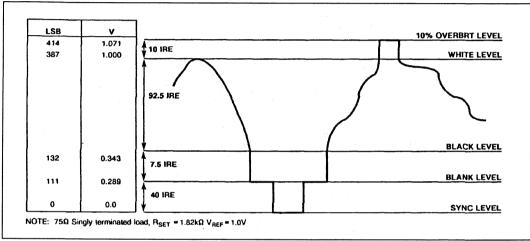

#### RS-343A and RS-170 Video Generation

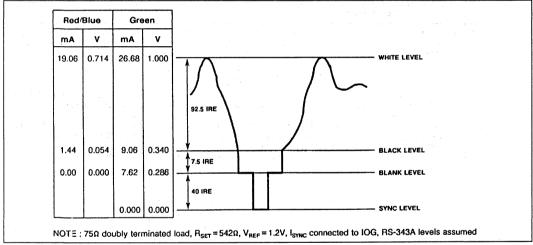

For generation of RS-343A compatible video levels (see Fig.4) it is recommended that a singly terminated 75 $\Omega$  load be used with an R<sub>SET</sub> resistor value of approximately 1.82k $\Omega$  Similarly for the generation of RS-170 video levels a

Similarly for the generation of RS-170 video levels a singly terminated  $75\Omega$  load should be used but in association with an  $R_{SET}$  value of approximately 1.29k $\Omega$  to provide the increased voltage range.

#### Non-Video Applications

The MV95308 may be used in non-video applications as explained in the pin description for STRDAC mode. The relationship between  $R_{SET}$  and the full scale output current has been explained previously and for a singly terminated  $75\Omega$  load an  $R_{SET}$  resistor value of approximately 1.19k $\Omega$  should be used.

#### PCB LAYOUT CONSIDERATIONS

The PCB layout should provide low noise on the MV95308 power and ground lines by shielding the digital inputs and providing adequate decoupling. The PCB should utilise both power and ground planes for best performance, connecting both planes to their respective regular PCB planes through a ferrite bead located as close as possible to the device. For best performance, a 100nF capacitor should be used to decouple the reference and supply pins. Decoupling should take place as close to the device as possible to reduce lead inductance. The digital inputs to the device should be isolated as much as possible from the analog outputs and other analog circuitry and should not overlay the analog ground and power planes.

To reduce noise pick-up, long clock lines to the device should be avoided. For best performance the analog output should have a  $75\Omega$  load connected to analog ground.

Fig.4 Composite video output waveform

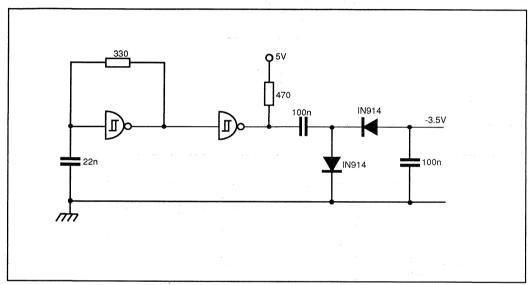

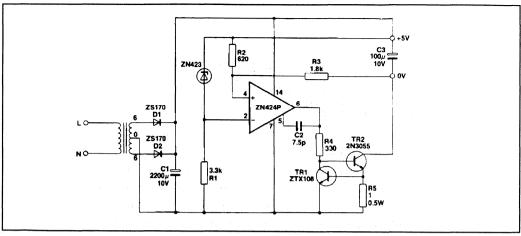

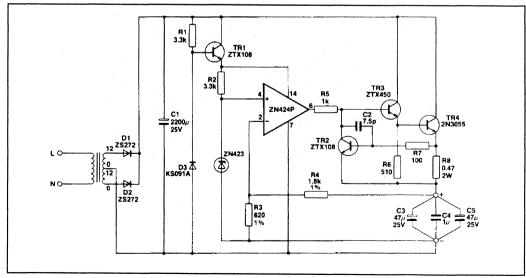

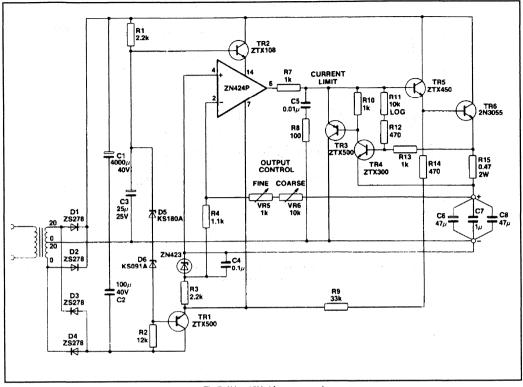

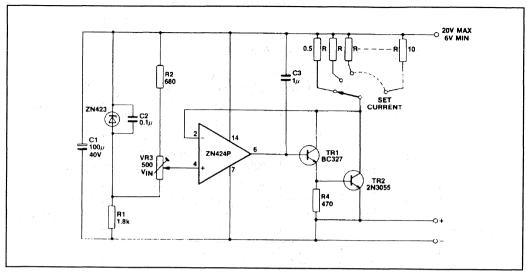

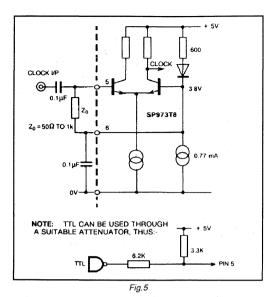

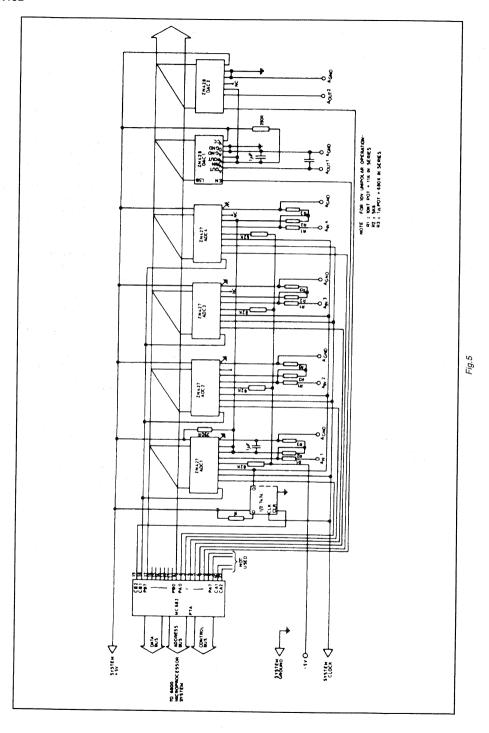

Fig.5 Applications/test board

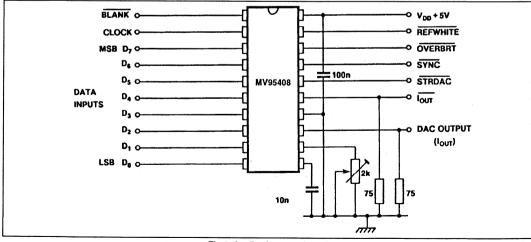

## MV95408 50MHz 8-BIT CMOS VIDEO DAC

The MV95408 is a CMOS 8-bit, 50MHz Digital to Analog converter, designed for use in both video graphics and general digital television applications.

A very low external component count has been achieved by including the loop amplifier and reference voltage source on chip.

The device contains a data input register and registered video controls (BLANK, REFWHITE, OVERBRT and SYNC). These control inputs and associated internal circuitry allows the MV95408 to be used in video graphics systems by providing the necessary video pedestal levels. The STRDAC input allows the video pedestals to be disabled in conventional DAC applications.

This device is capable of directly driving  $75\Omega$  lines with standard RS-343A or RS-170 video levels, using the appropriate  $R_{SFT}$  external resistor.

Pull up resistors have been added to tie all unused control inputs into their inactive (High) states.

#### **FEATURES**

- Low Power Consumption (180mW Typ)

- 50MHz Pipeline Operation

- ±1 LSB Differential Linearity Error

- ±1 LSB Integral Linearity Error

- RS-343A/RS-170 Compatible Levels

- On Chip Reference Voltage Source

- Guaranteed Monotonic

- Drives 75Ω Loads Directly

- Single 5V Power Supply

#### **ORDERING INFORMATION**

MV95408 BDP (Industrial - Plastic DIL Package)

MV95408 BMP (Industrial - Miniature Plastic DIL

Fig.1 Pin connections - top view

#### **APPLICATIONS**

- Data Conversion (general)

- Computer Graphics

- Waveform Synthesis

- Commercial TV

- Instrumentation

#### ABSOLUTE MAXIMUM RATINGS (Reference to GND)

DC Supply Voltage, V<sub>DD</sub>

Digital Input Voltage

Analog Output Short Circuit Duration

Ambient Operating Temperature

Storage Temperature Range

-0.3 to +7V -0.3 to V<sub>DD</sub> +0.3V Indefinite -40°C to +85°C -55°C to +125°C

Fig.2 Block diagram of MV95408

#### **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless otherwise stated):

As specified in recommended operating conditions. Full temperature range = -40°C to +85°C

DC CHARACTERISTICS

| Parameter                                      | Symbol            | Temp<br>(°C) | Min.         | Value<br>Typ. | Max.                 | Units      | Conditions                                  |

|------------------------------------------------|-------------------|--------------|--------------|---------------|----------------------|------------|---------------------------------------------|

| Resolution                                     |                   | Full         | 8            |               |                      | Bits       |                                             |

| Integral linearity error                       | INL               | 25<br>Full   |              | ±0.5          | ±1                   | LSB<br>LSB | 1.<br>1.1                                   |

| Differential linearity error                   | DNL               | 25<br>Full   |              | ±0.5          | ±1                   | LSB<br>LSB |                                             |

| Gain error                                     |                   | 25           |              | ±1%           | ±5%                  | %          | Of full scale                               |

| Analog output                                  |                   |              | ^ '          | - 1           |                      |            |                                             |

| Grey scale current range                       |                   | 25           |              | 8.8<br>255    | -                    | mA<br>LSB  |                                             |

| 10% Over Bright level relative to White level  |                   | 25           | 26           | 27<br>10      | 28                   | LSB<br>IRE | 4 1                                         |

| White level relative to Blank level            |                   | 25           | 275          | 276<br>100    | 277                  | LSB<br>IRE | 75Ω singly                                  |

| Black level relative to Blank level            |                   | 25           | 20           | 21<br>7.5     | 22                   | LSB        | terminated load<br>R <sub>SET</sub> = 1.8kΩ |

| White level relative to Black level            |                   | 25           |              | 255<br>92.5   |                      | LSB        | (graphics mode)                             |

| Blank level                                    | 1                 | 25           | 107          | 111<br>40     | 115                  | LSB        |                                             |

| Sync level                                     |                   | 25           |              | 0             |                      | LSB        |                                             |

| LSB size                                       | LSB               | 25           |              | 2.58          | ,                    | m۷         |                                             |

| Output compliance                              | V <sub>oc</sub>   | 25           | -0.3         |               | +1.5                 | V          | <b>[</b> ] .                                |

| Digital inputs                                 |                   |              |              |               |                      |            |                                             |

| High level I/P voltage                         | V <sub>IH</sub>   | 25           | 3            |               | V <sub>DD</sub> +0.3 | ٧          |                                             |

| Low level I/P voltage                          | V <sub>II</sub> . | 25           | GND-0.3      |               | 1.2                  | V          |                                             |

| High level I/P current                         | I <sub>IH</sub>   | 25           |              | 1.0           | +1                   | μA         |                                             |

| Low level I/P current                          | lii.              | 25           |              |               | -1                   | μA         |                                             |

| Internal voltage reference (V <sub>REF</sub> ) | V <sub>REF</sub>  | 25<br>Full   | 0.95<br>0.90 | 1.0           | 1.05<br>1.10         | V          |                                             |

| V <sub>REF</sub> temperature coefficient       | *                 |              |              | 40            |                      | ppm/°C     |                                             |

#### AC CHARACTERISTICS (Refer to Fig. 3)

| Parameter                                                                                                                 | Symbol                              | Temp<br>(°C)               | Min.   | Value<br>Typ.                    | Max. | Units                                | Conditions                  |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------|--------|----------------------------------|------|--------------------------------------|-----------------------------|

| Max clock rate                                                                                                            | f <sub>MAX</sub>                    | Full                       | 50     |                                  |      | MHz                                  | maximum<br>guaranteed freq. |

| Clock high time<br>Clock low time                                                                                         | t <sub>CLKH</sub>                   | 25<br>25                   | 7<br>7 | <i>F</i>                         | ·    | ns<br>ns                             |                             |

| Data and control setup time<br>Data and control hold time                                                                 | t <sub>SU</sub>                     | 25<br>25                   | 6<br>2 |                                  | e    | ns<br>ns                             |                             |

| Analog output delay Analog output rise/fall time Analog output settling time Glitch energy V <sub>DD</sub> supply current | t <sub>DLY</sub> t <sub>RF</sub> ts | 25<br>25<br>25<br>25<br>25 |        | 10<br>3<br>15<br>100<br>30<br>42 | 6    | ns<br>ns<br>ns<br>pV-sec<br>mA<br>mA | fc = 15MHz<br>fc = 50MHz    |

| THERMAL | CHAR | ACTERI | STICS |

|---------|------|--------|-------|

| Thermal Resistance              | DP | MP |      |

|---------------------------------|----|----|------|

| Chip to case θ <sub>iC</sub>    | 20 | 30 | °C/W |

| Chip to ambient θ <sub>iA</sub> | 75 | 93 | °C/W |

#### RECOMMENDED OPERATING CONDITIONS

| 75Ω            |

|----------------|

| $.0V \pm 0.5V$ |

| 1.8kΩ          |

| 1.2kΩ          |

|                |

#### CIRCUIT DESCRIPTION

As illustrated in the function block diagram, Fig. 2, the MV95408 contains an 8-bit D-to-A converter, input registers, a loop amplifier and voltage reference.

On the falling edge of each clock cycle, as shown in Fig. 3, eight data bits are latched into the device and passed to the 8-bit D-to-A converter. Also latched on the falling edge of the clock signal, the SYNC and BLANK inputs add the necessary weighted currents to the analog outputs to produce the required output levels for use in video applications. Table 1 details how the SYNC, BLANK, REFWHITE and OVERBRT inputs modify the DAC output levels

To obtain a high data throughput rate, the decoding logic of the MV95408 is fully pipelined. This introduces a one clock cycle delay between the latching of the input data and the resultant DAC output.

It also ensures synchronisation of the internal data and a minimal output glitch energy.

The DAC employed by the MV95408 eliminates the need for precision component ratios by using a segmented architecture in which equal weight bit currents are either routed to lour or lour. The use of identical current sources and current steering their outputs means that monotonicity is guaranteed.

The MV95408 eliminates the need for an external voltage reference by providing a nominally 1.0V reference on chip. An on-chip loop amplifier also provides stability of the full scale output current against power supply and temperature variations. The full scale output current is set by an external resistor R<sub>SET</sub>. By adjustment of this value it is possible to implement RS-343A or RS-170 video levels as explained in the application notes.

Fig.3 Timing diagram

| Description    | STRDAC | SYNC | BLANK | REFWHITE | OVERBRT | OUTPUT<br>DATA | l <sub>out</sub><br>(LSB) |

|----------------|--------|------|-------|----------|---------|----------------|---------------------------|

| REFWHITE + 10% | 1      | 1    | 1     | 0        | 0       | Х              | 414                       |

| REFWHITE       | 1      | 1    | 1     | 0        | 1       | Х              | 387                       |

| FULL WHITE     | 1      | . 1  | 1     | 1        | 1       | \$FF           | 387                       |

| OVERBRIGHT     | 1      | 1    | 1     | 1        | 0       | DATA           | DATA +<br>132 + 27        |

| FULL BLACK     | 1      | 1    | 1     | 1        | 1       | \$00           | 132                       |

| BLANK          | 1      | 1    | 0     | Х        | Х       | Х              | 111                       |

| DATA-SYNC      | 1      | 0    | 1     | 1        | 1       | DATA           | DATA + 21                 |

| SYNC           | 1      | 0    | 0     | х        | Х       | X              | 0                         |

| STRDAC MODE    | 0      | Х    | 1     | . 1      | Х       | DATA           | DATA                      |

Table 1: Video output truth table

| Pin   | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2     | CLK                                 | The clock input. The falling edge of the clock latches the DATA, BLANK, SYNC, OVERBRT and REFWHITE inputs into the logic pipeline. The decoded data will be latched into the DAC output 1 clock cycle later. The clock frequency determines the update rate of the DAC output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3-10  | D <sub>7</sub> -D <sub>0</sub>      | The data inputs. D <sub>0</sub> is the least significant bit (LSB). The coding is in straight binary only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13,15 | l <sub>ουτ</sub> , l <del>ουτ</del> | The current output and its complement. These are the high impedance current source outputs of the DAC capable of driving a 75 $\Omega$ load up to a voltage of 1.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14    | GND                                 | Analog ground for the DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20    | V <sub>DD</sub>                     | Analog power for the DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11    | V <sub>REF</sub>                    | The output of the internal voltage reference generator. This output is nominally 1V, and should be decoupled with a 10nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12    | R <sub>SET</sub>                    | The full scale adjust control. The R <sub>SET</sub> resistor is connected from this pin to ground. An internal loop amplifier adjusts a reference current flowing through the R <sub>SET</sub> resistor so that the voltage across the resistor is equal to the V <sub>REF</sub> voltage. This reference current has a weighting equal to 16 LSB's.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1     | BLANK                               | The composite blank control input. A logical zero on this input removes the Black pedestal from the I <sub>OUT</sub> output, whilst forcing the internal data to the DAC to \$00. This input is latched on the clock falling edge and will override the REFWHITE and OVERBRT inputs. The Black pedestal is 7.5 IRE units (actually 21 LSB's). If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17    | SYNC                                | The composite sync control input. A logical zero on this input removes the Blank pedestal from the lour output. The Blank pedestal is nominally 40 IRE units (actually 111 LSB's). The SYNC input does not override any other control lines. This input is latched on the clock falling edge. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19    | REFWHITE                            | The reference white level control input. A logical zero on this input overrides the input data, forcing the data to \$FF. The BLANK input will override this input. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18    | OVERBRT                             | The 10% overbright control input. A logical zero on this input switches the Overbright pedestal into the I <sub>OUT</sub> output. The Overbright pedestal is 10 IRE units (actually 27 LSB's). This input does not override any other input. The BLANK input overrides this input. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16    | STRDAC                              | The straight DAC control input. A logical zero on this input causes the Black, Blank and Overbright pedestals to be disabled, removing them from both I <sub>OUT</sub> and I <sub>OUT</sub> . This allows the DAC contribution to the output to be extended to a full 1 Volt. To obtain this extra DAC range, it is necessary to reduce the R <sub>SET</sub> resistor value, see application notes. The BLANK the REFWHITE inputs may still be used to force the input data to \$00 or \$FF respectively. With the STRDAC pin held low the output current can be calculated from:  Output current = Data x 1 LSB  Where 1 LSB= V <sub>REF</sub> / 16 x R <sub>SET</sub> Full scale = 255 LSB  V <sub>REF</sub> = 1.0V typ.  The exact value of 1 LSB must be calculated from the full scale output. If left open circuit this input is internally tied high and the device will be configured for video graphics. In this mode the output current can be calculated from:  Output current = (DATA + 21 + 111) x 1 LSB  V <sub>REF</sub> = 1.0V typ. |

#### APPLICATIONS INFORMATION

#### RS-343A and RS-170 Video Generation

For generation of RS-343A compatible video levels (see Fig.4) it is recommended that a singly terminated  $75\Omega$  load be used with an  $R_{\rm SFT}$  resistor value of approximately  $1.82 k\Omega$

Similarly for the generation of RS-170 video levels a singly terminated 75 $\Omega$  load should be used but in association with an  $R_{SET}$  value of approximately 1.29k $\Omega$  to provide the increased voltage range.

#### Non-Video Applications

The MV95408 may be used in non-video applications as explained in the pin description for  $\overline{\text{STRDAC}}$  mode.The relationship between  $R_{SET}$  and the full scale output current has been explained previously and for a singly terminated  $75\Omega$  load an  $R_{SET}$  resistor value of approximately 1.19k $\Omega$  should be used

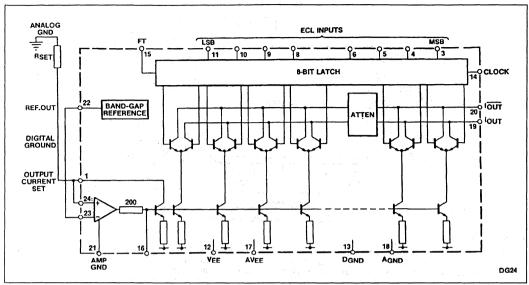

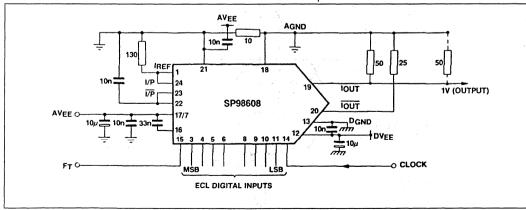

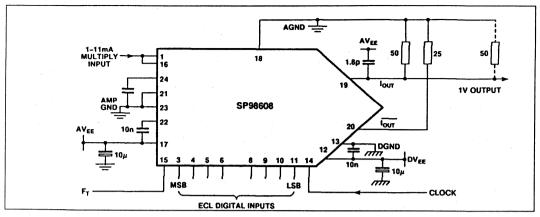

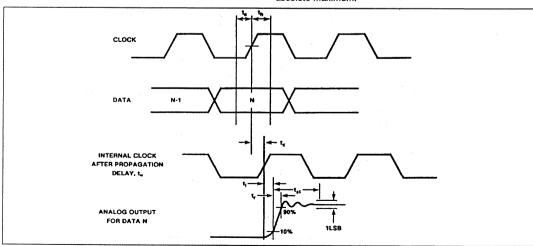

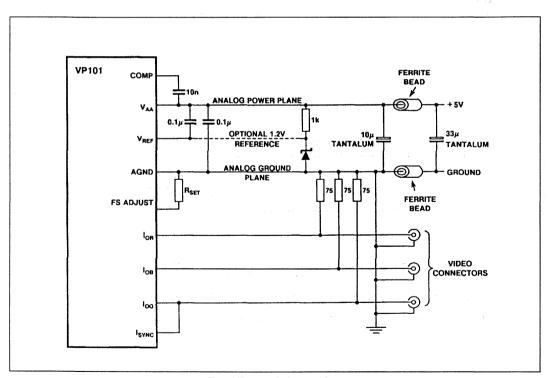

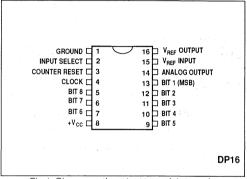

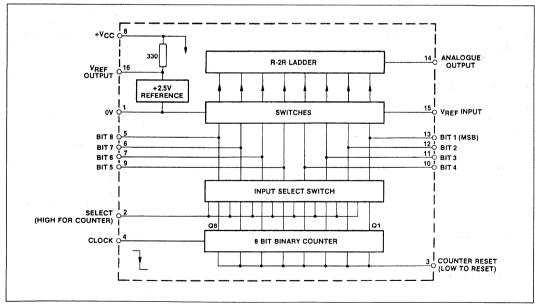

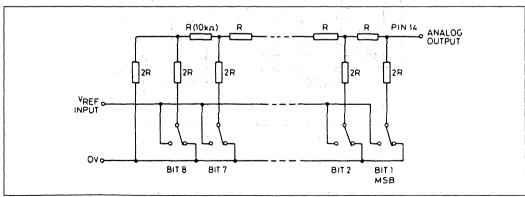

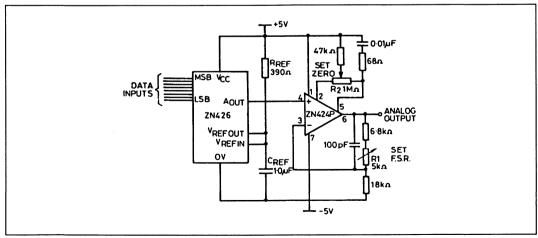

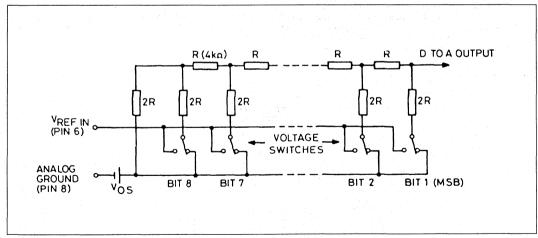

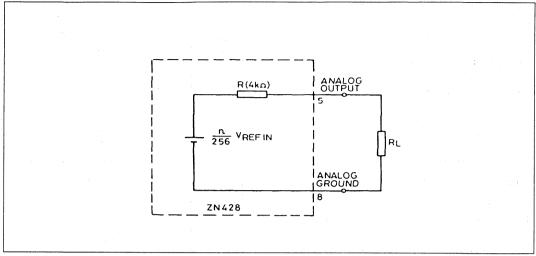

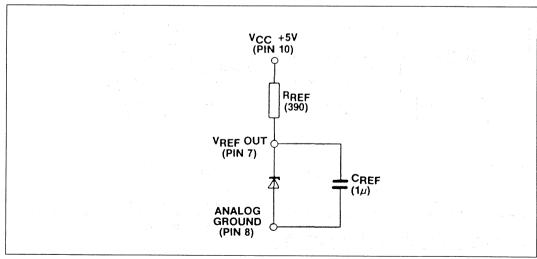

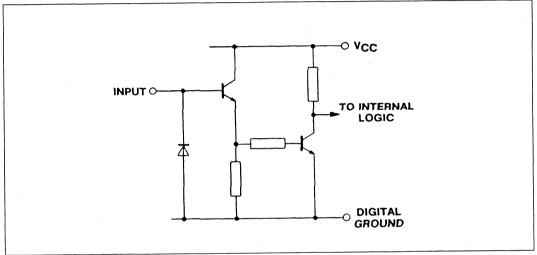

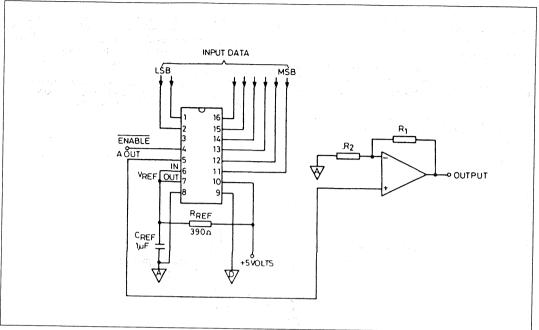

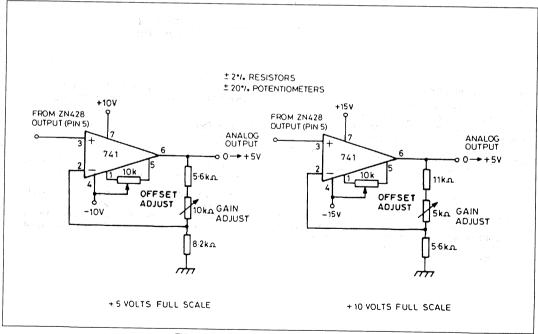

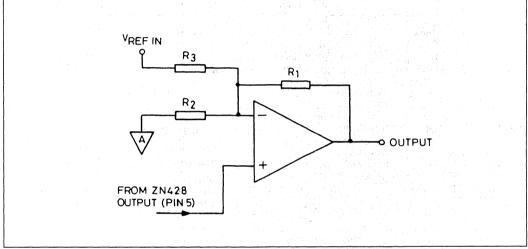

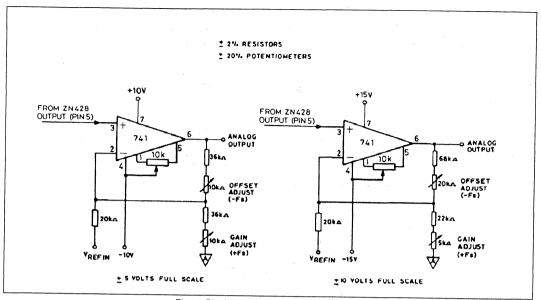

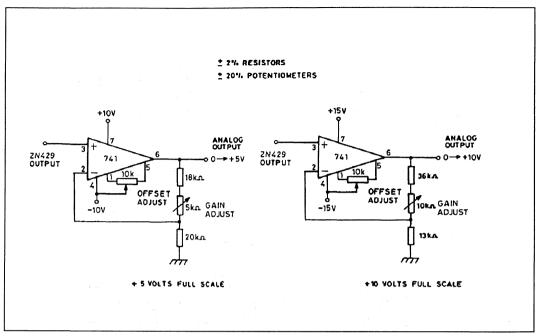

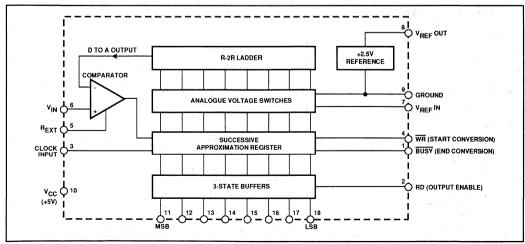

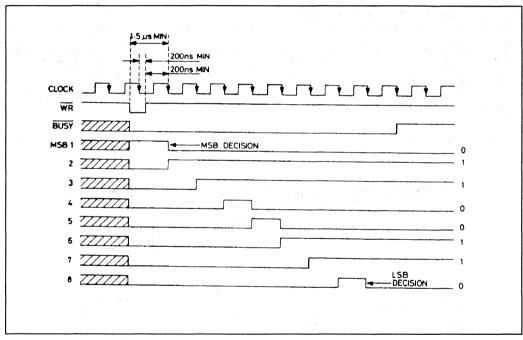

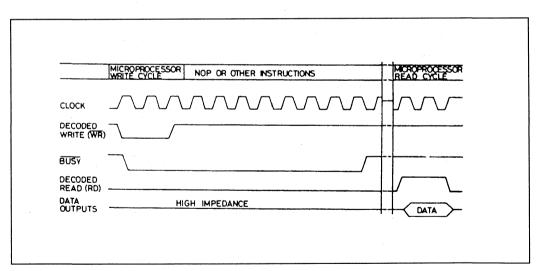

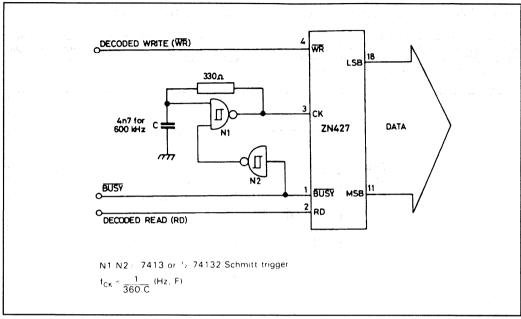

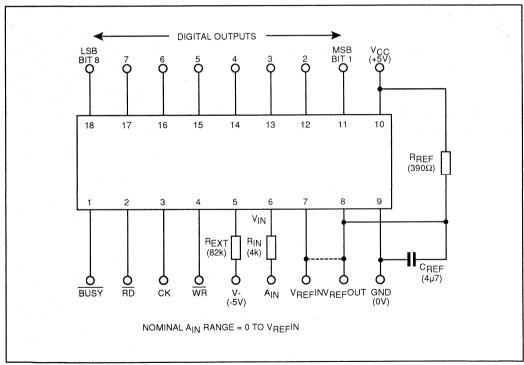

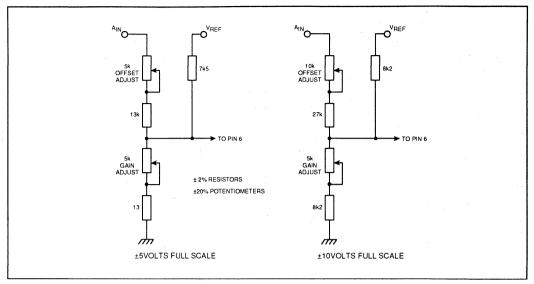

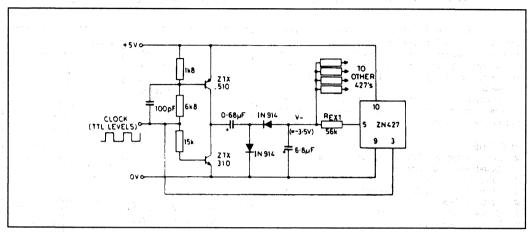

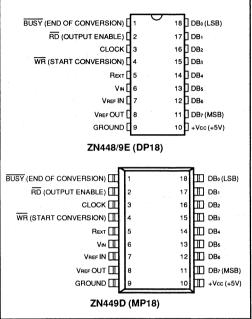

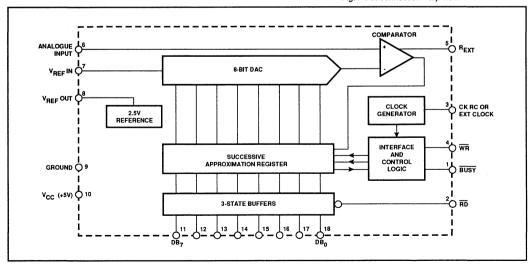

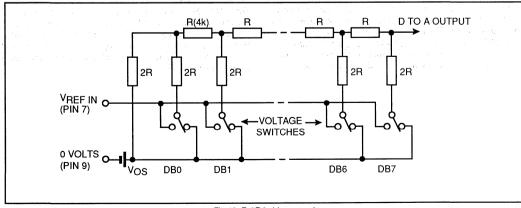

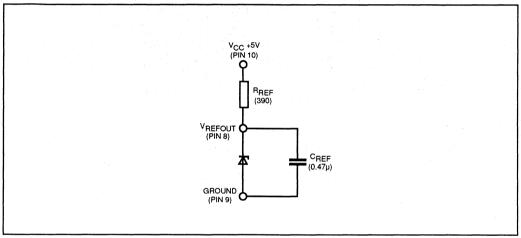

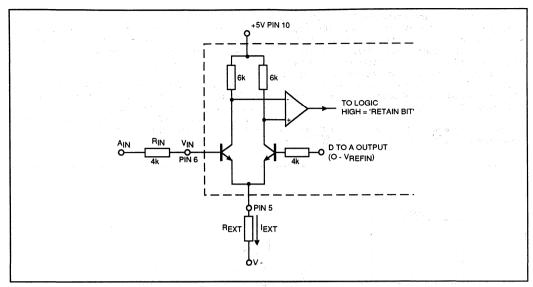

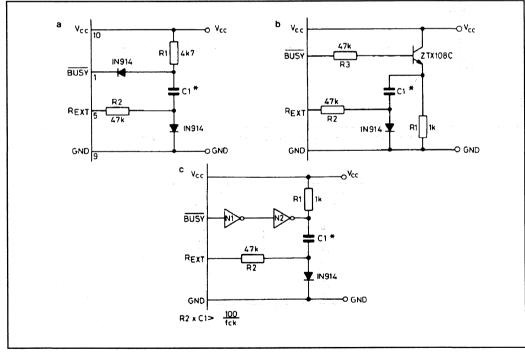

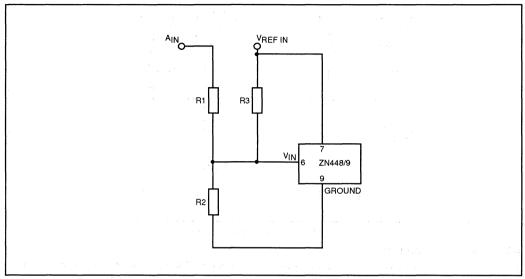

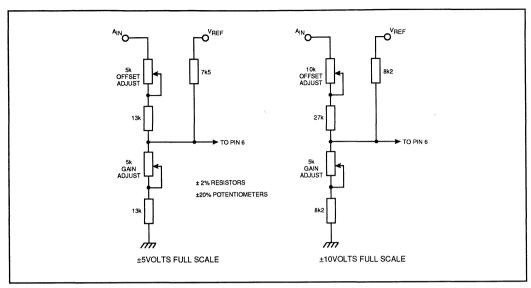

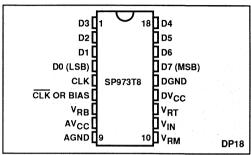

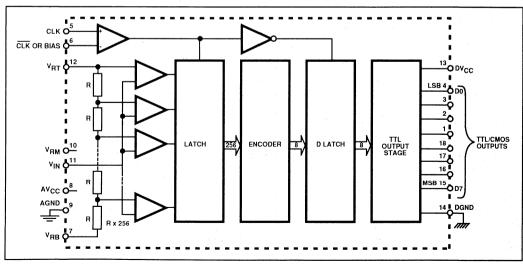

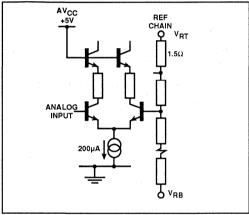

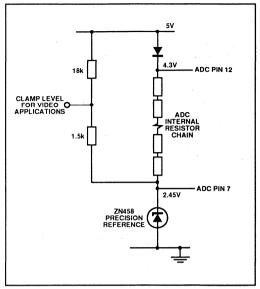

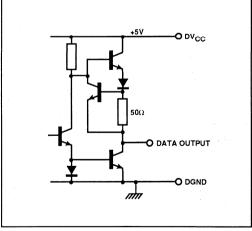

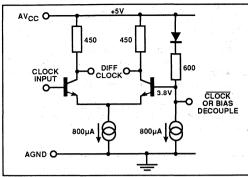

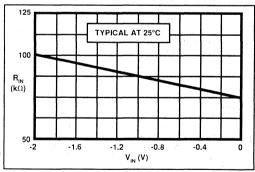

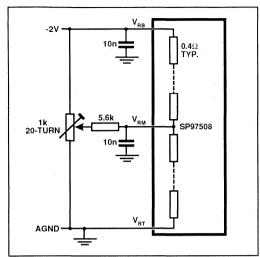

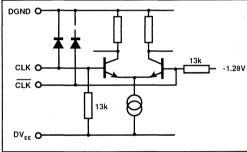

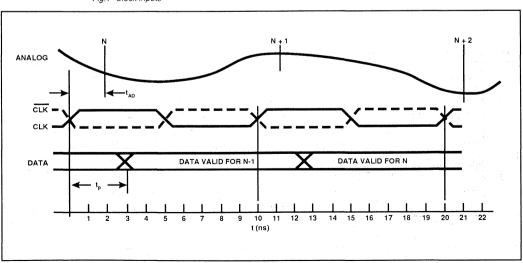

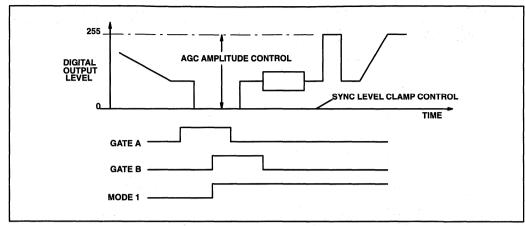

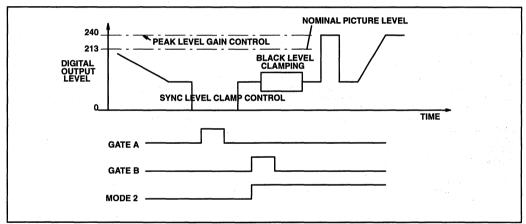

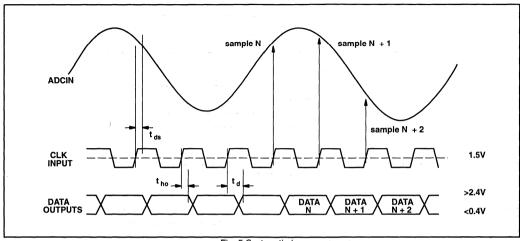

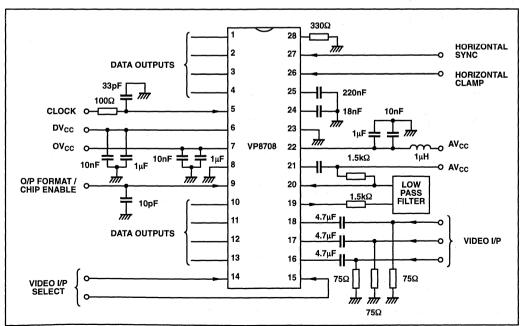

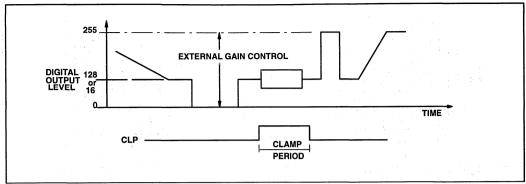

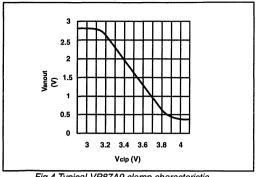

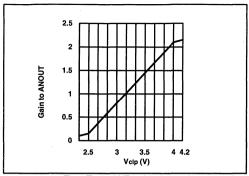

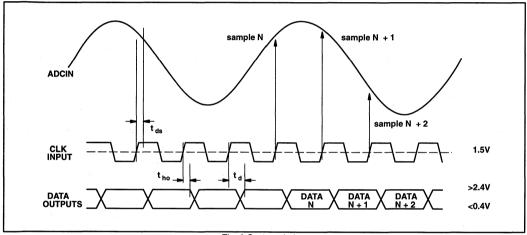

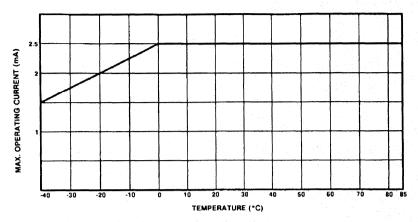

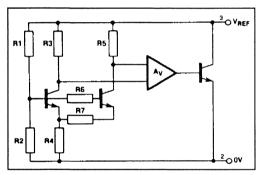

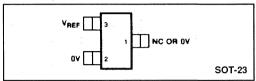

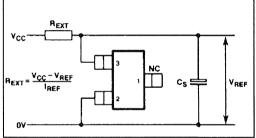

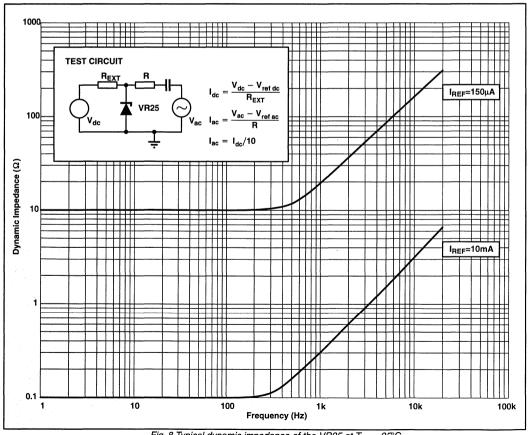

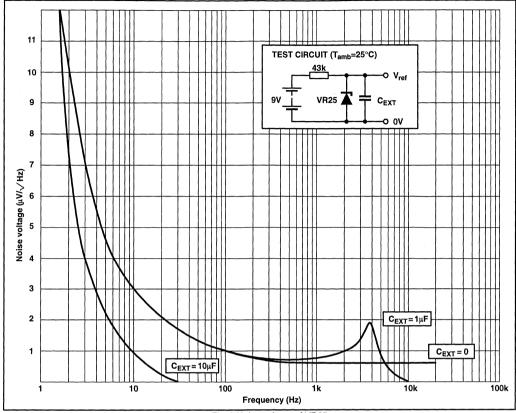

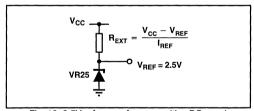

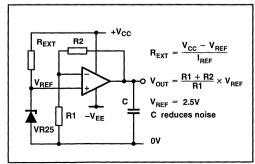

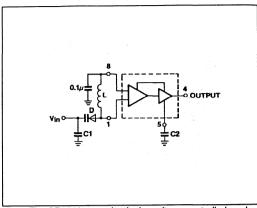

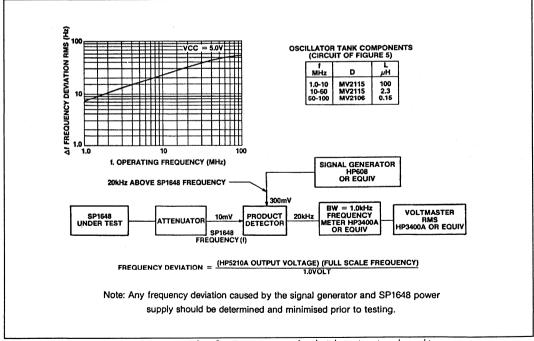

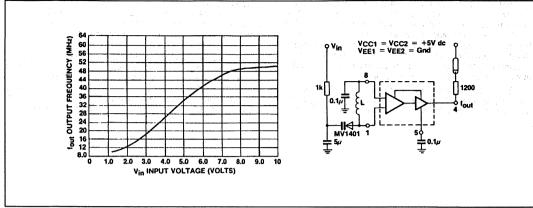

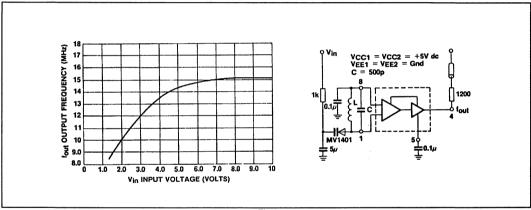

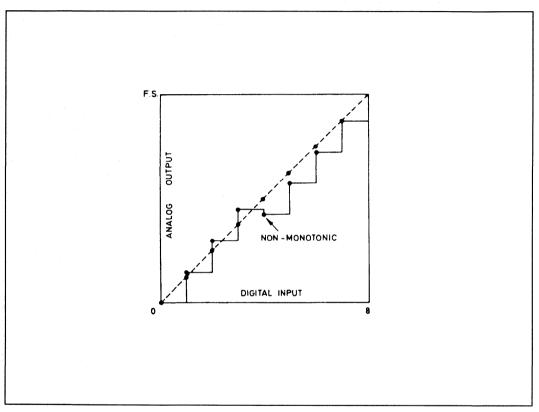

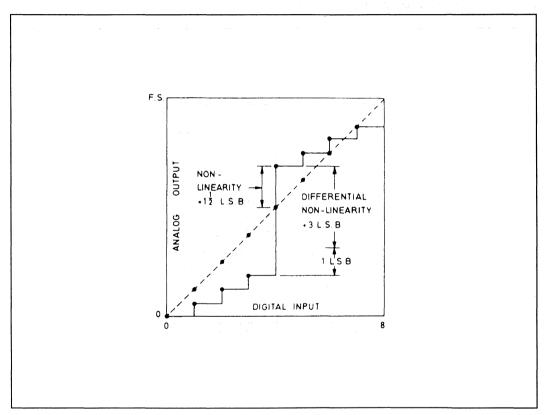

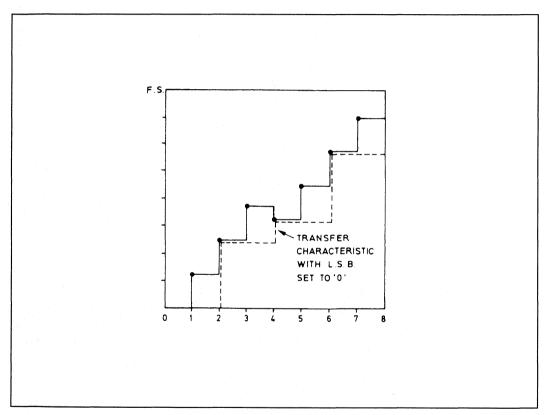

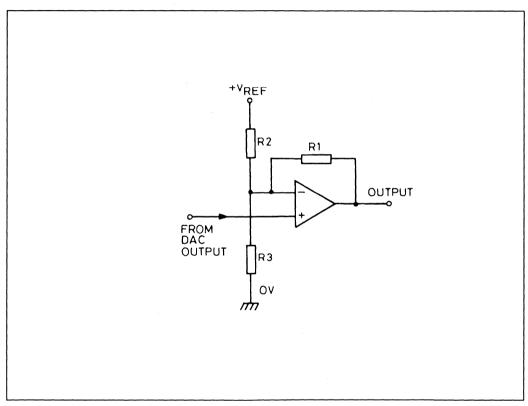

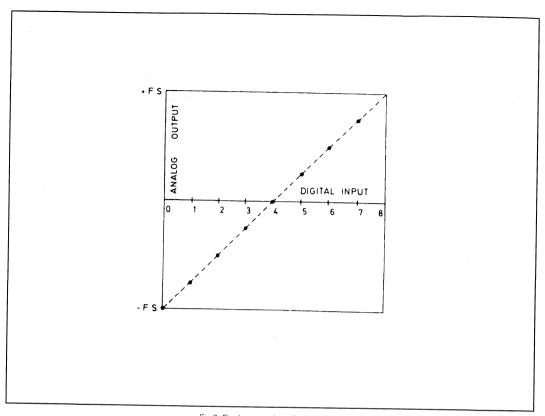

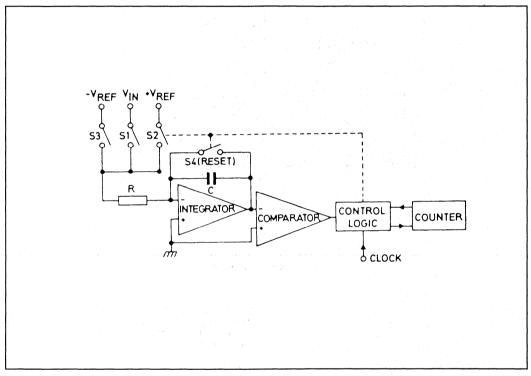

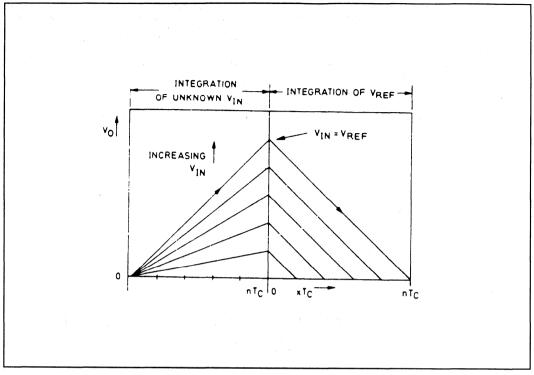

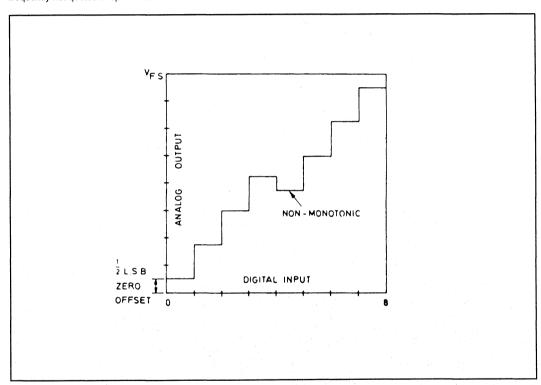

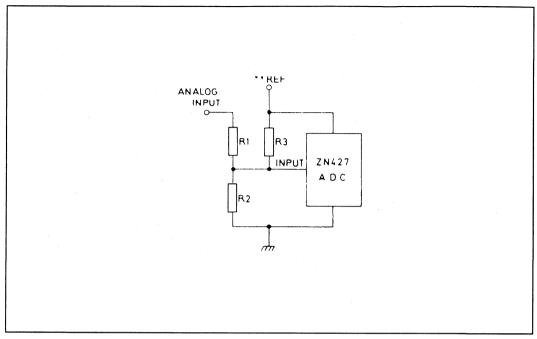

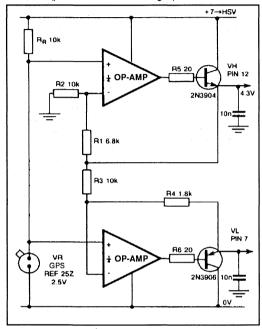

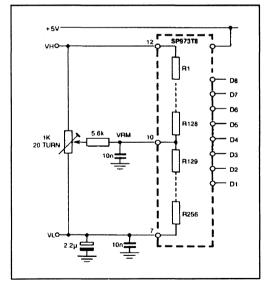

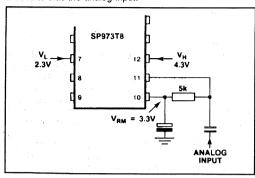

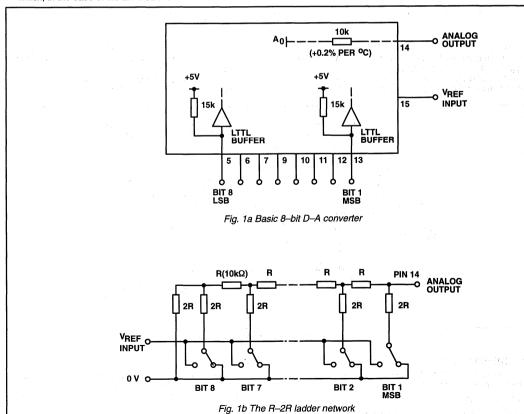

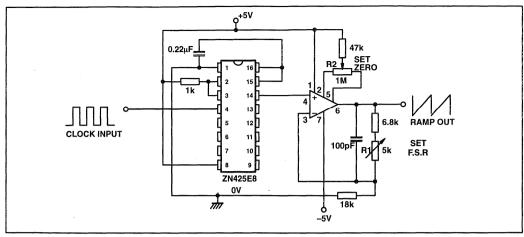

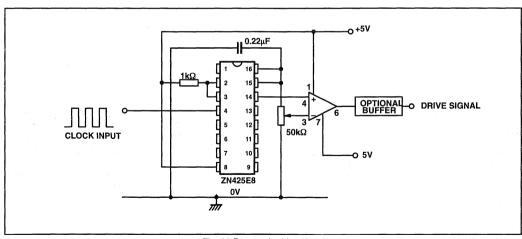

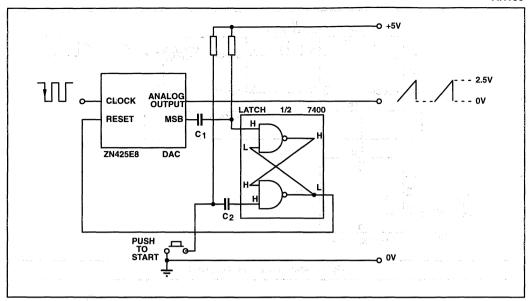

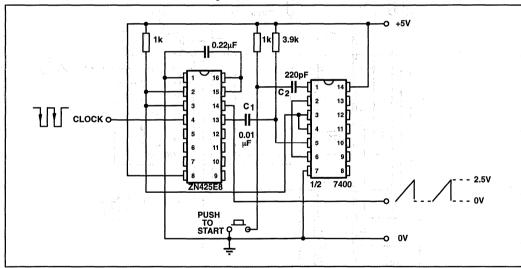

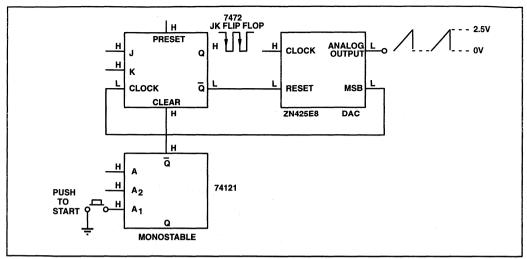

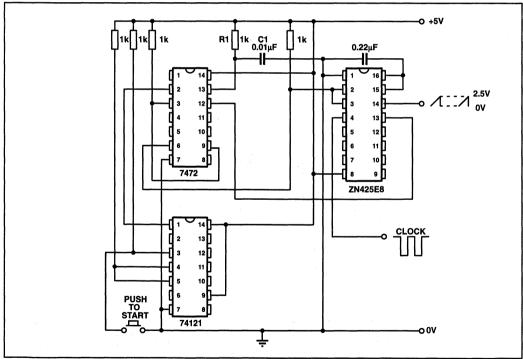

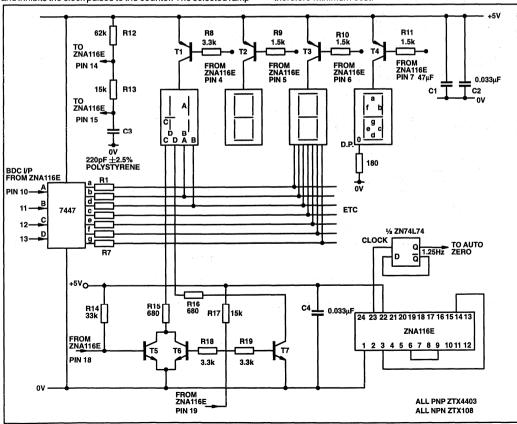

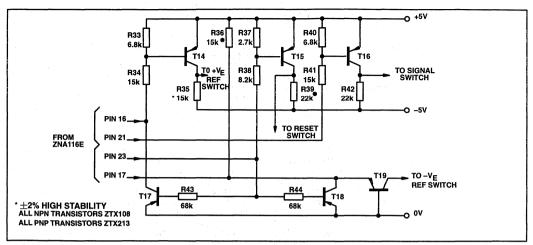

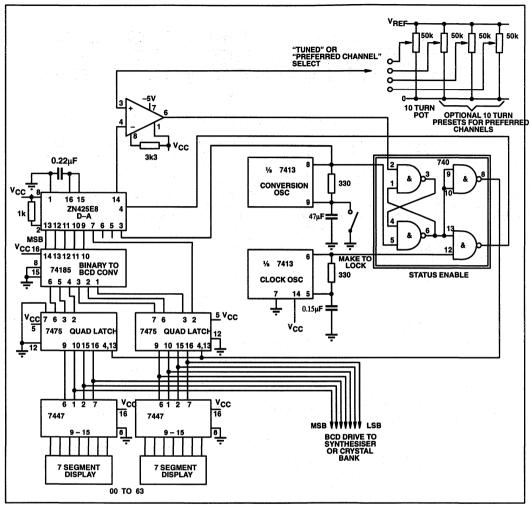

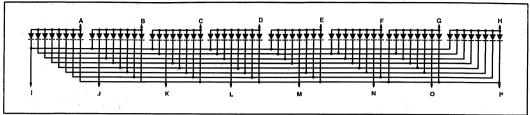

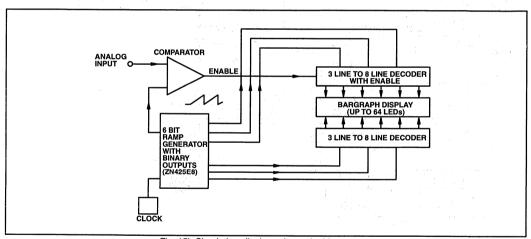

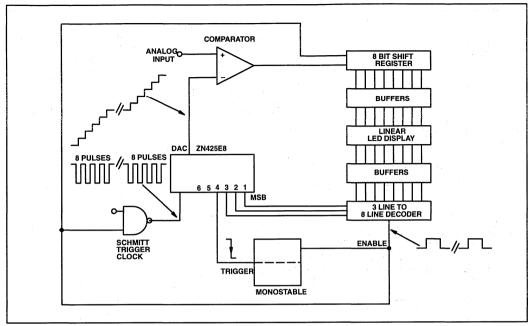

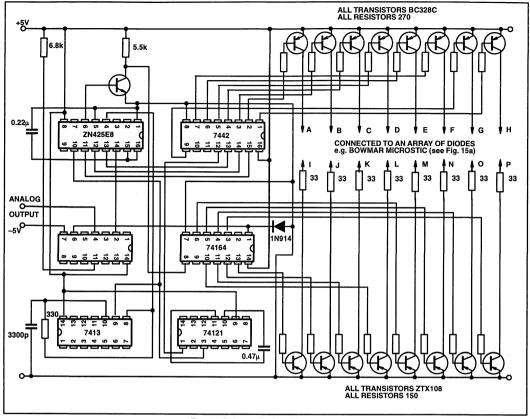

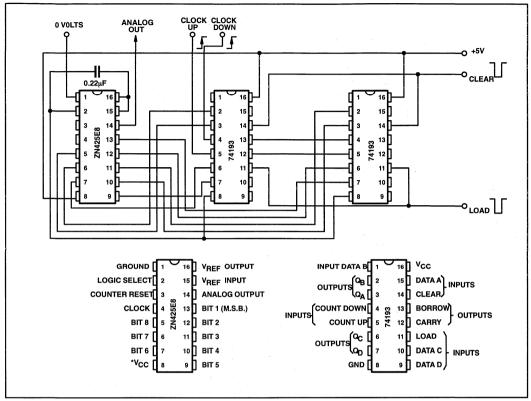

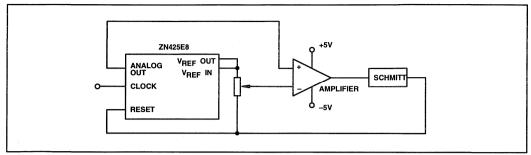

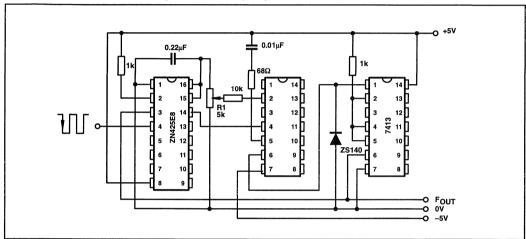

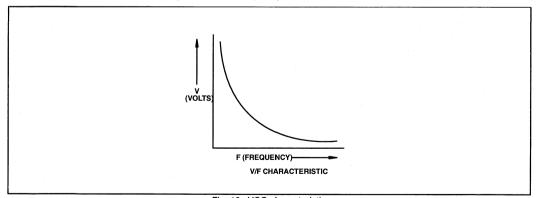

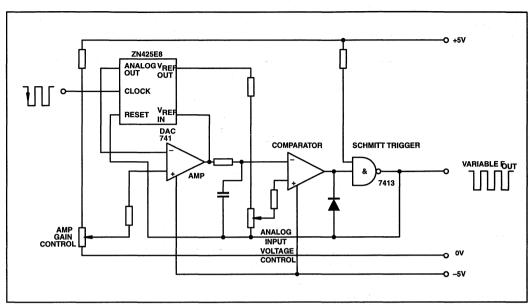

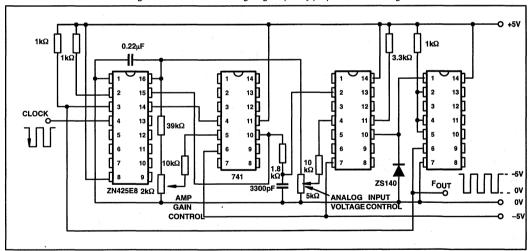

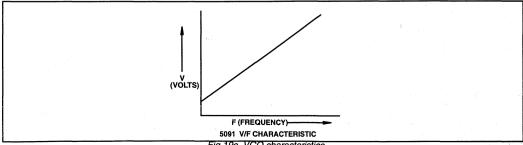

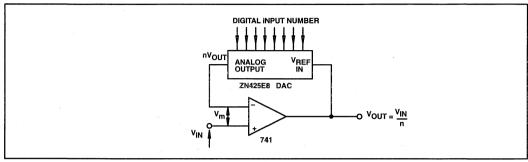

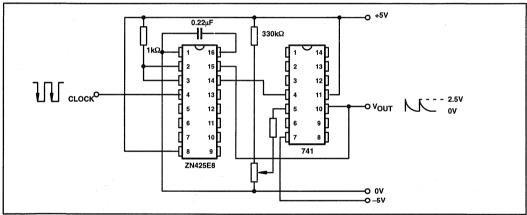

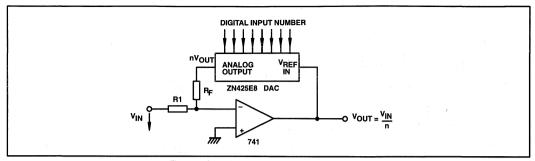

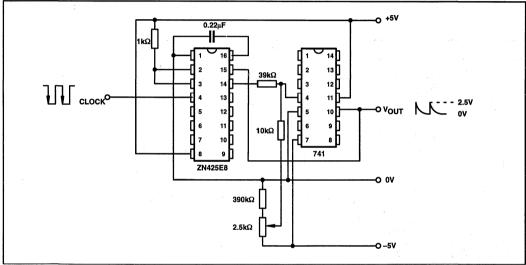

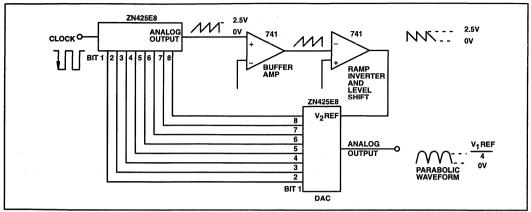

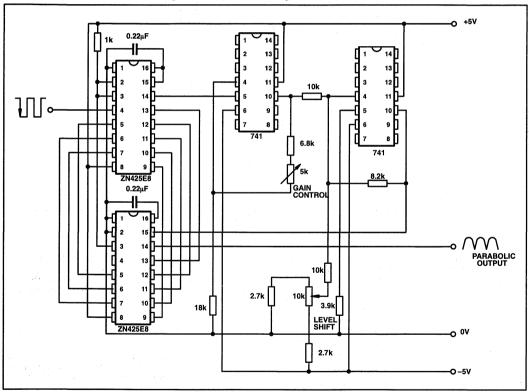

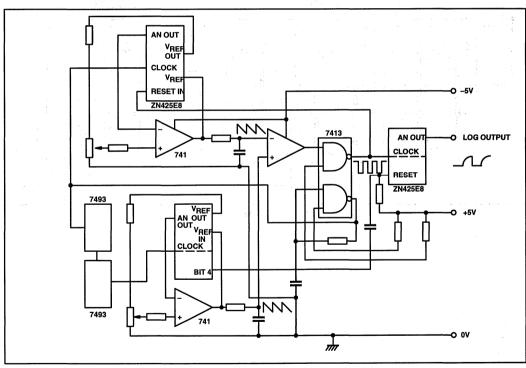

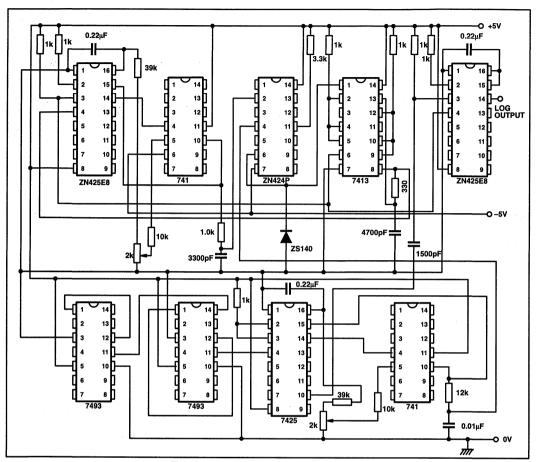

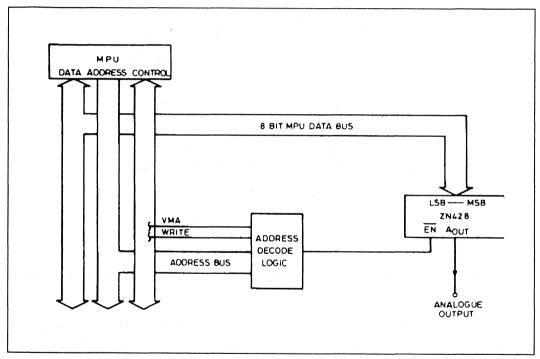

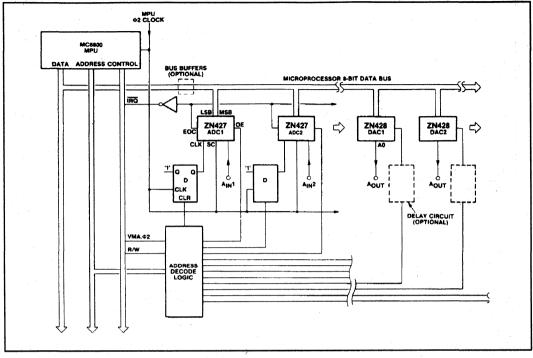

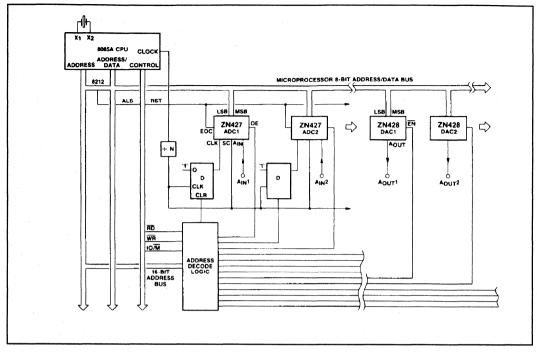

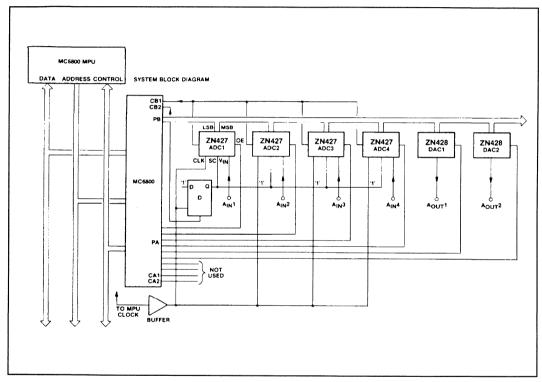

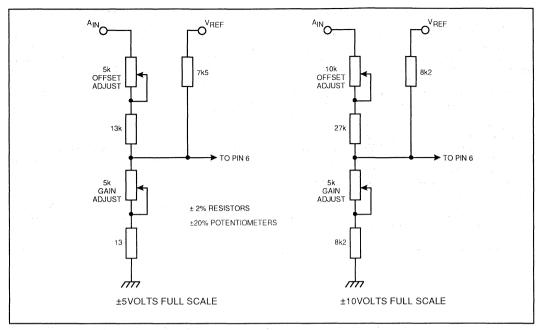

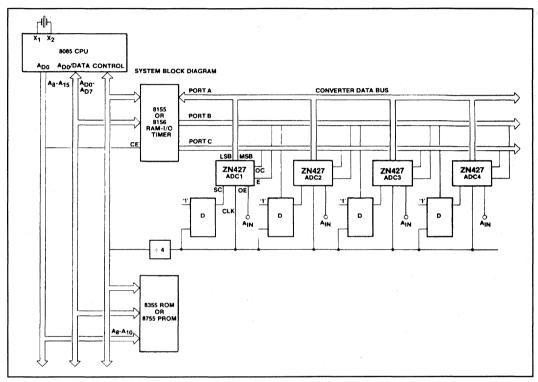

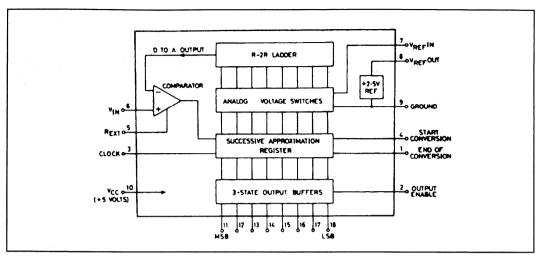

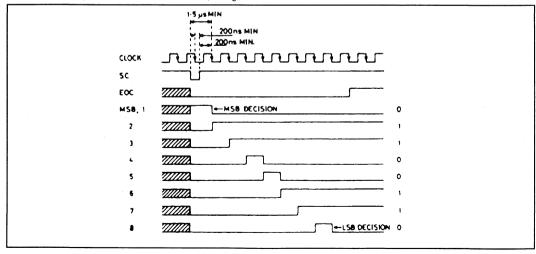

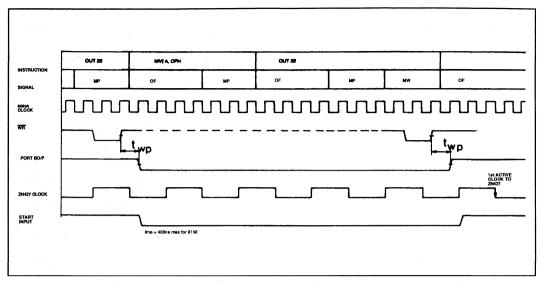

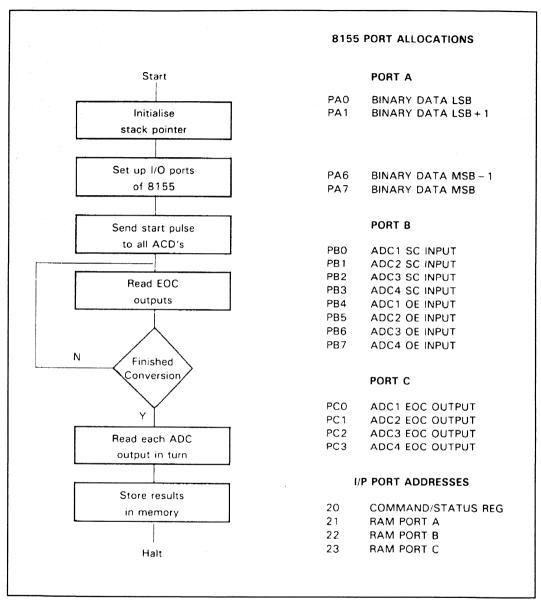

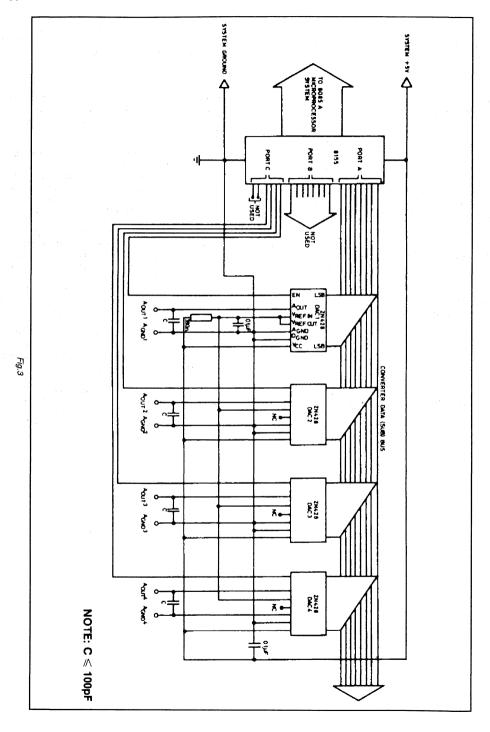

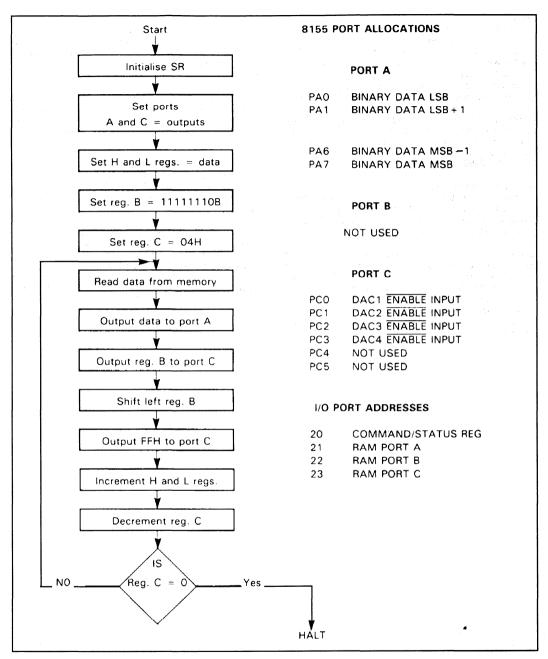

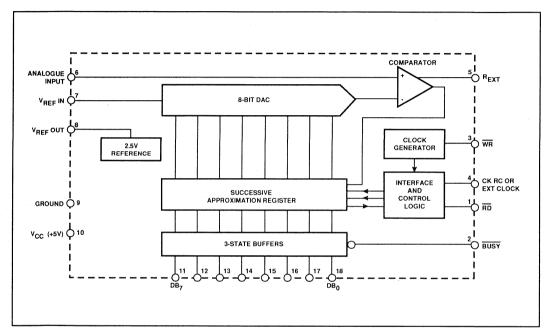

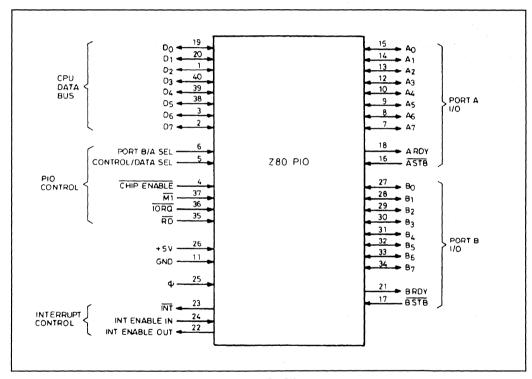

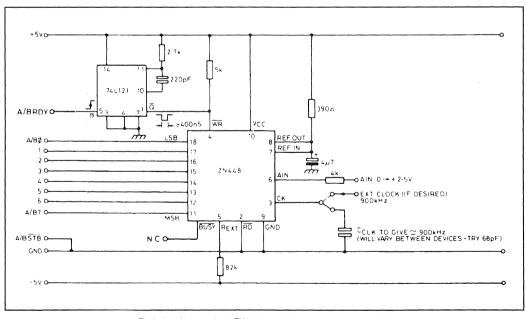

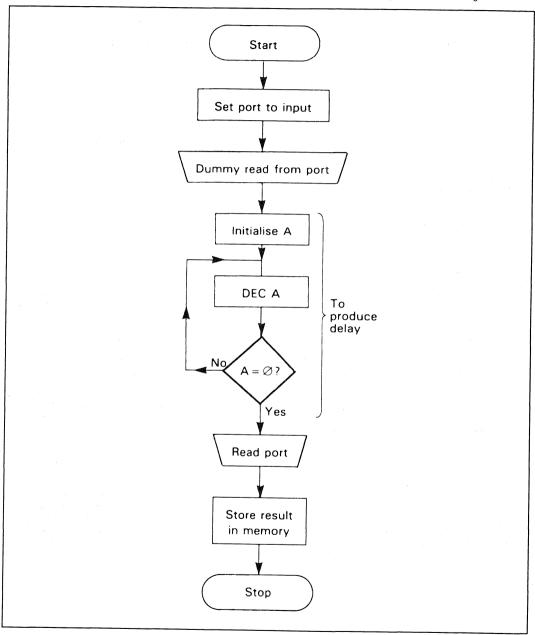

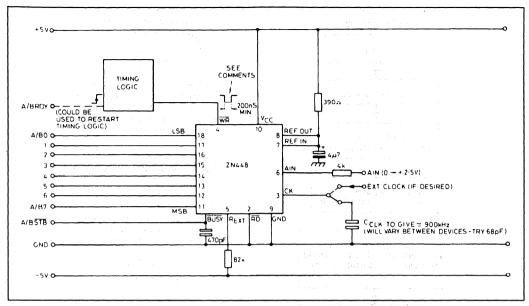

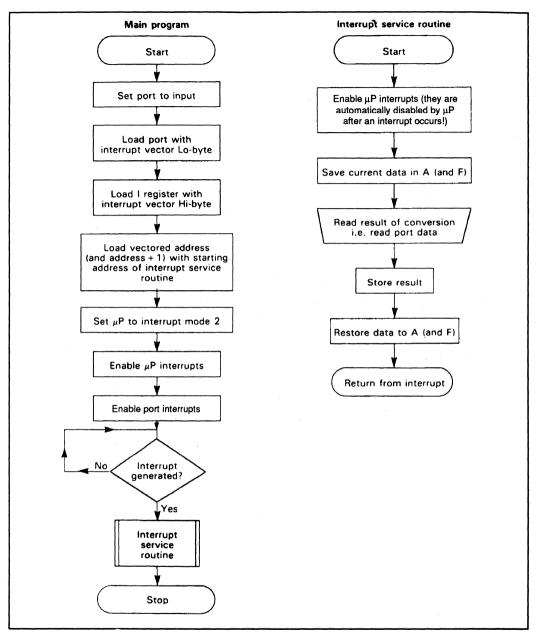

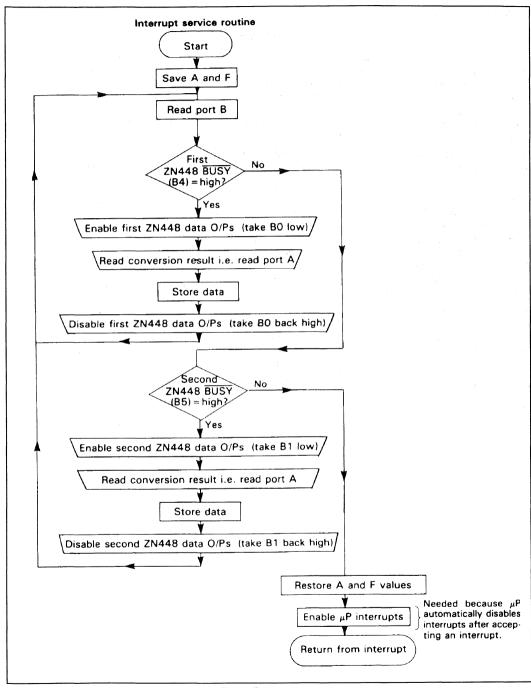

#### **PCB LAYOUT CONSIDERATIONS**